Hi,

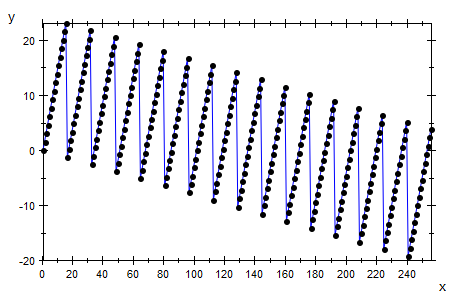

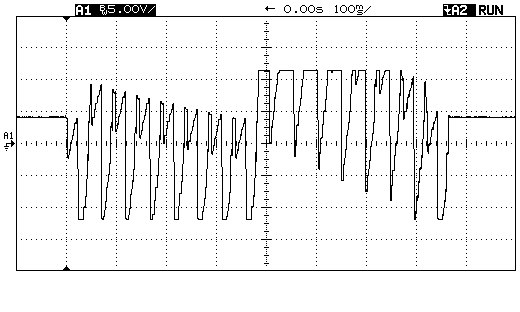

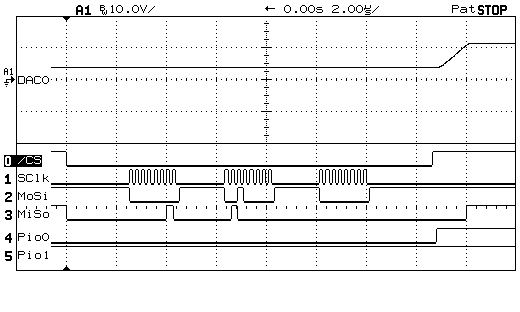

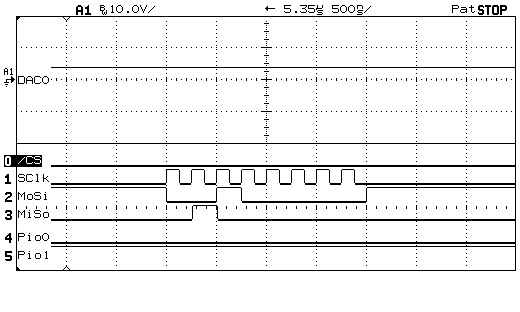

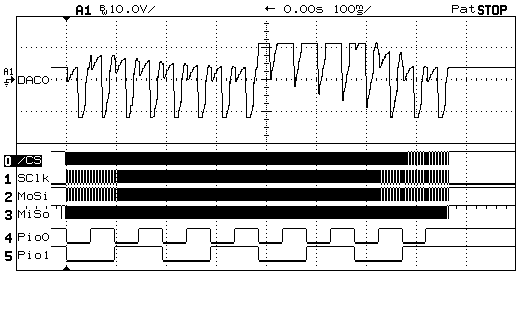

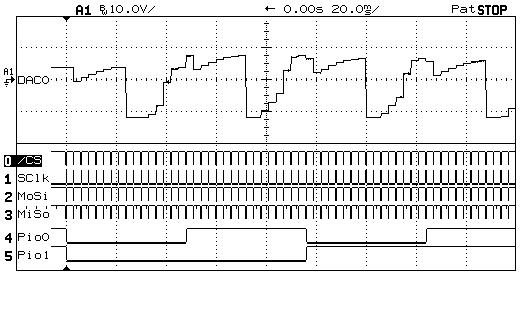

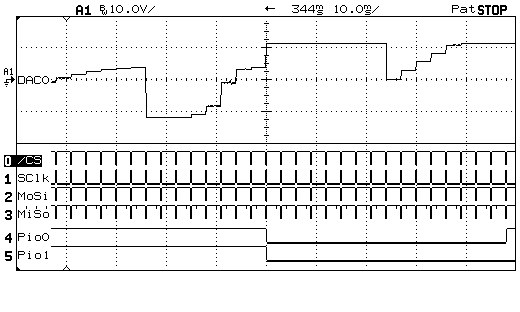

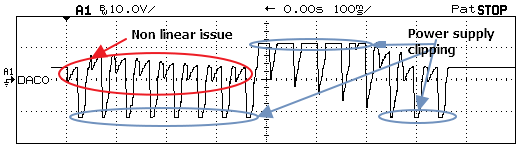

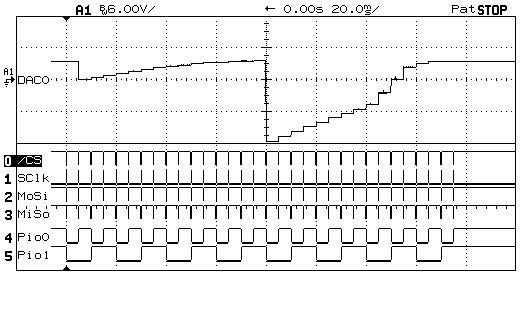

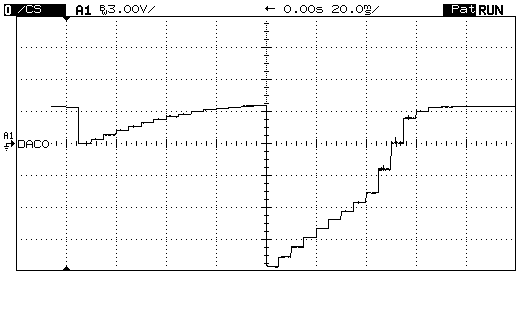

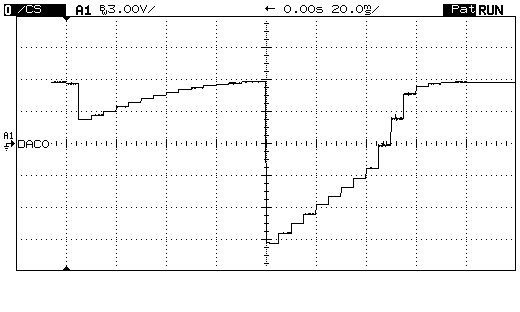

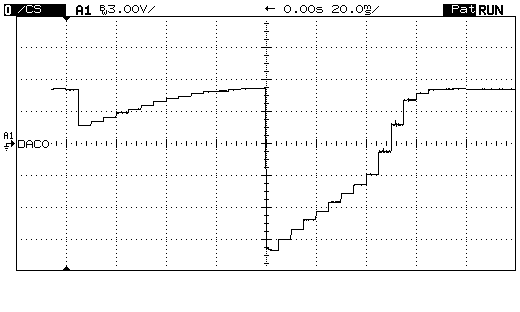

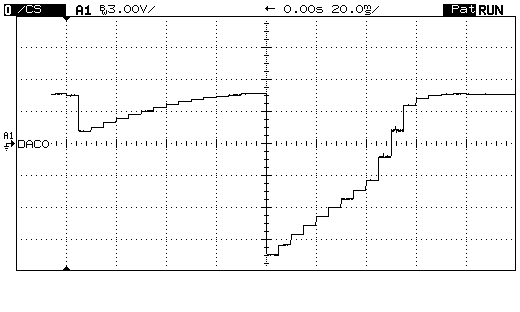

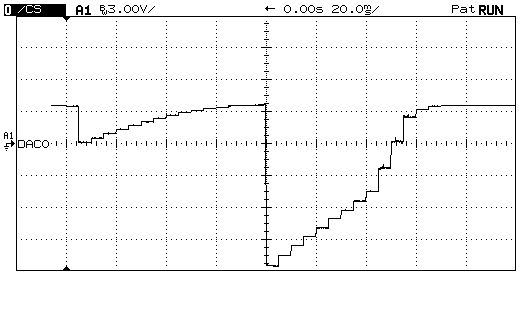

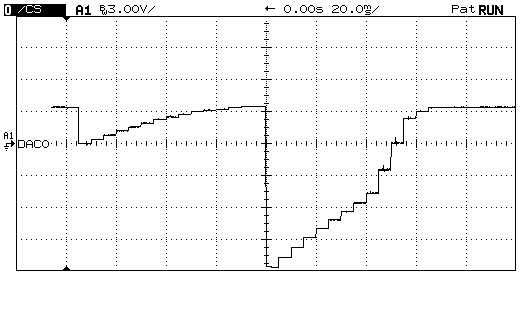

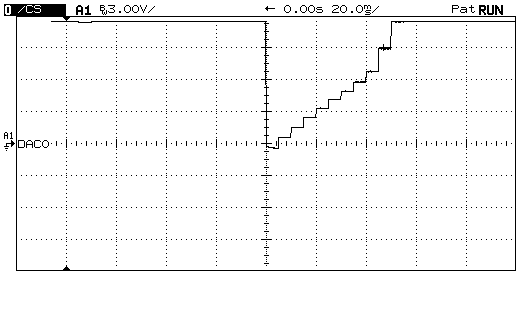

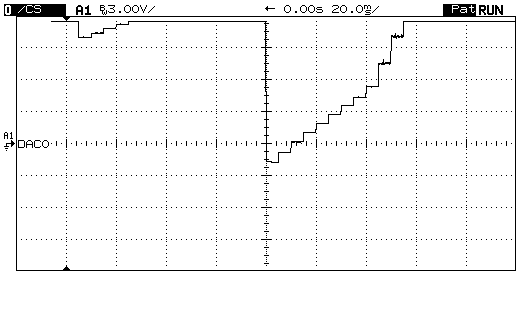

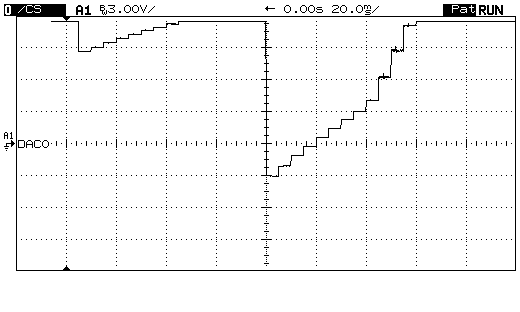

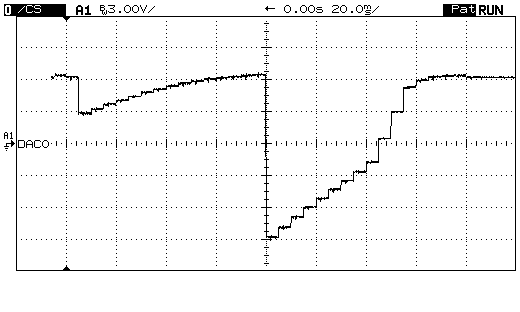

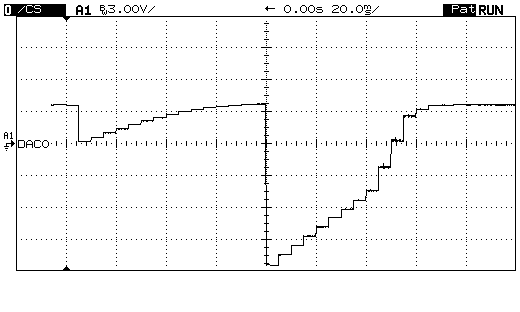

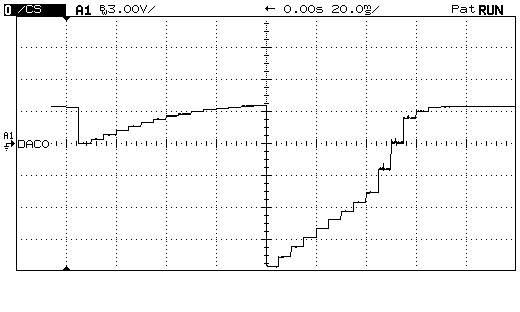

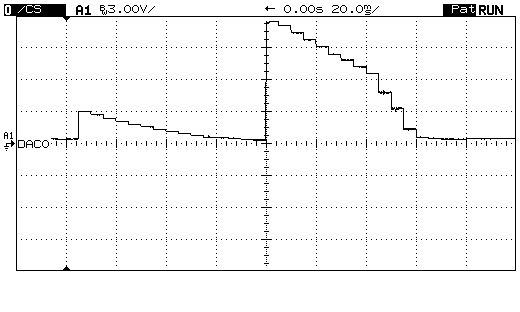

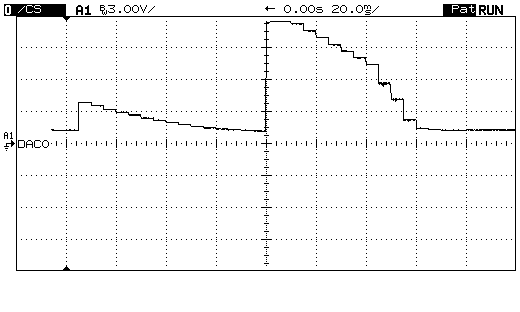

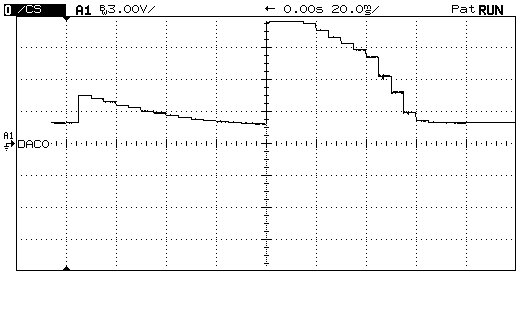

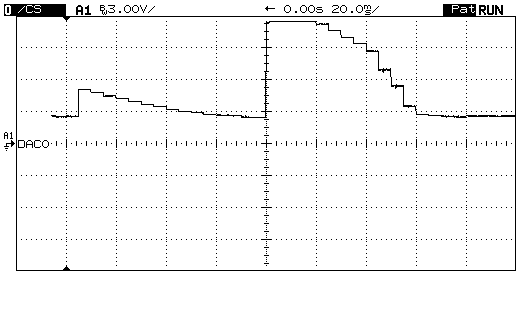

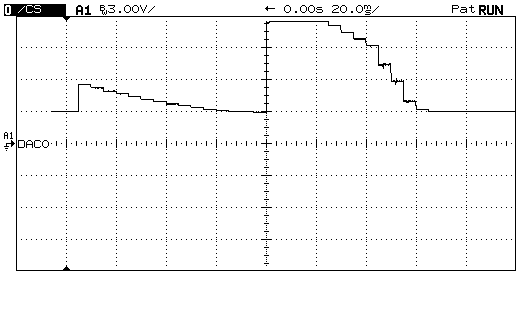

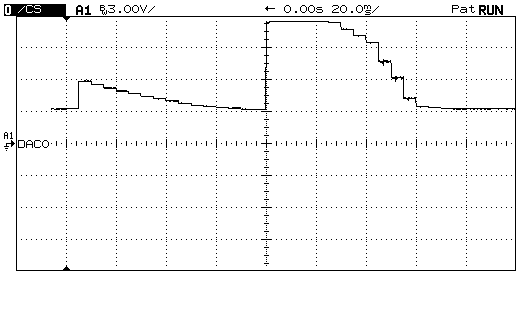

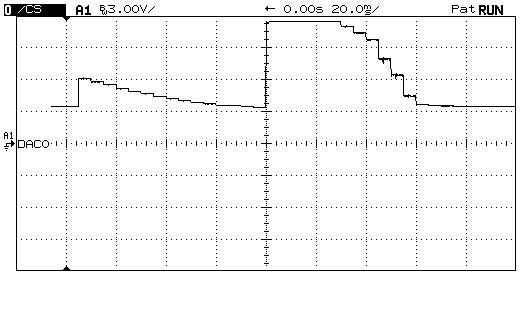

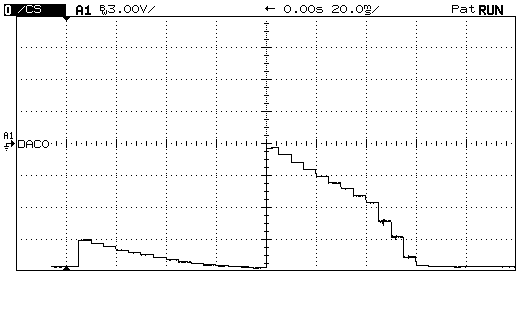

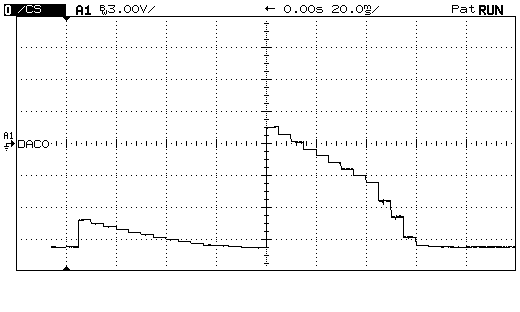

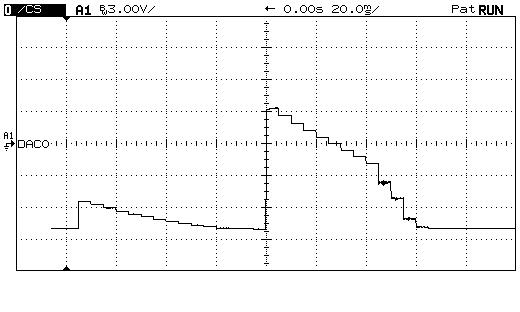

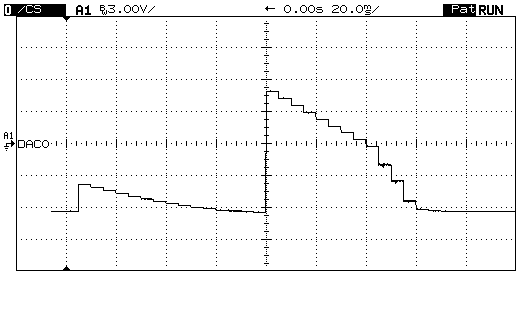

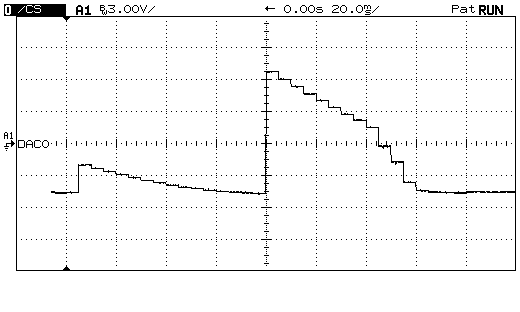

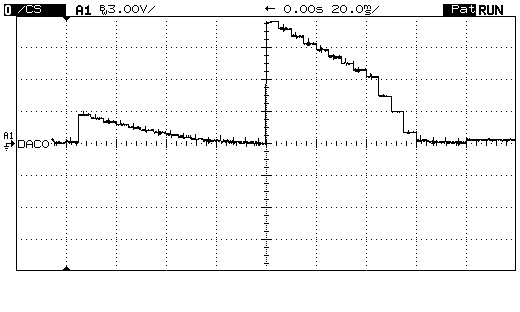

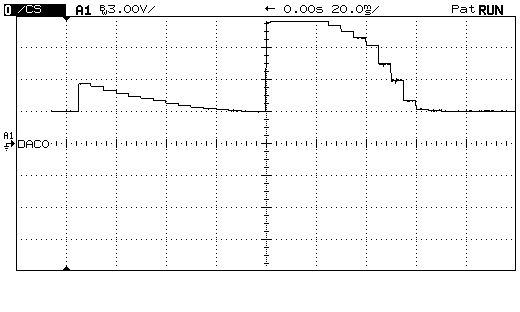

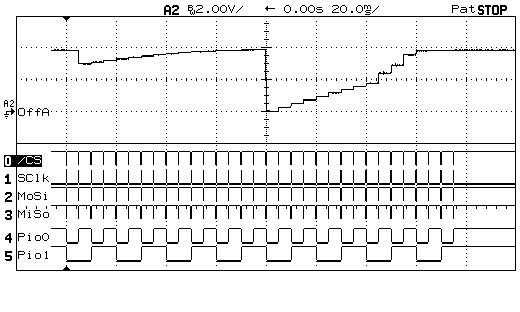

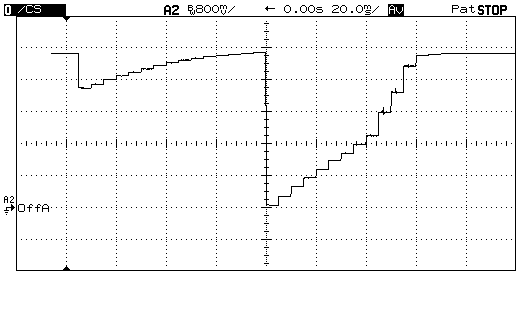

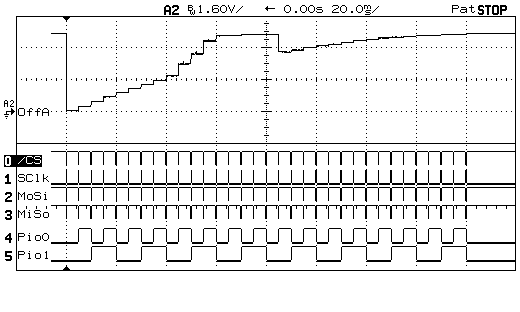

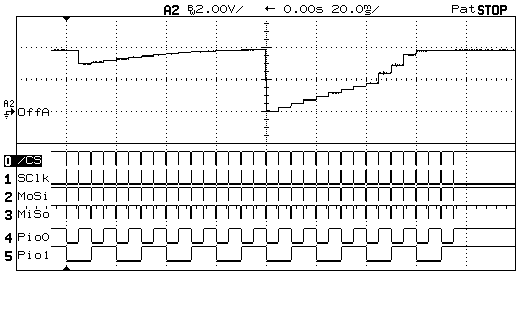

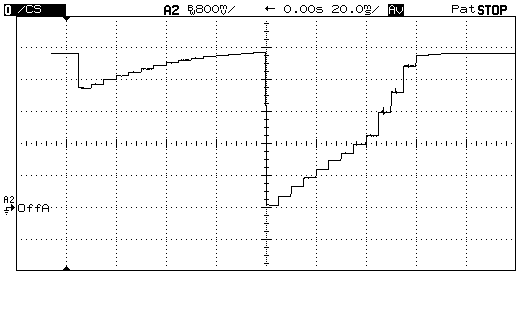

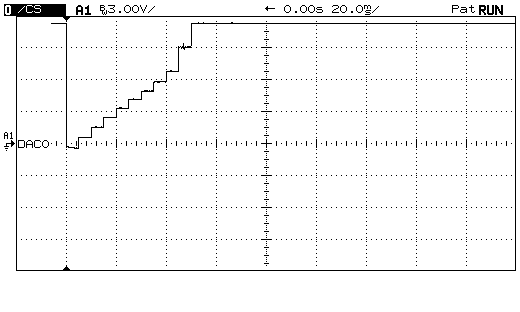

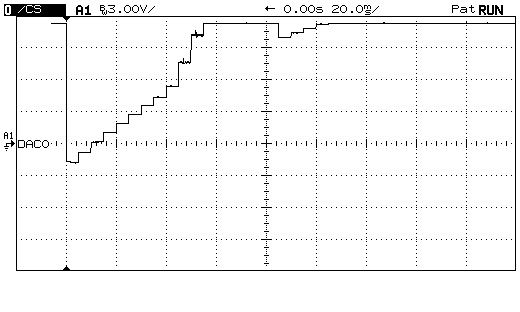

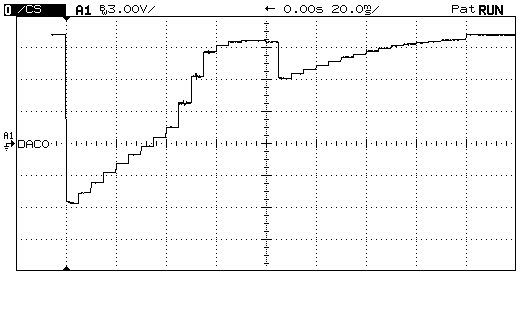

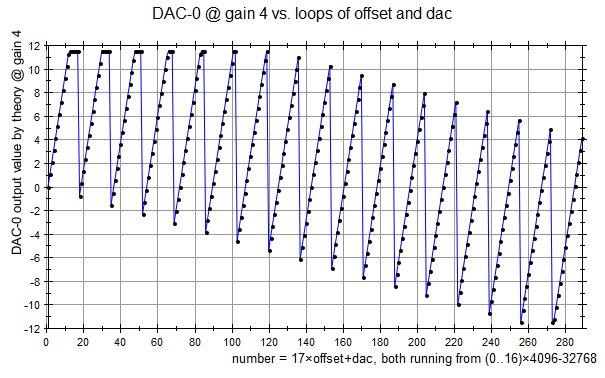

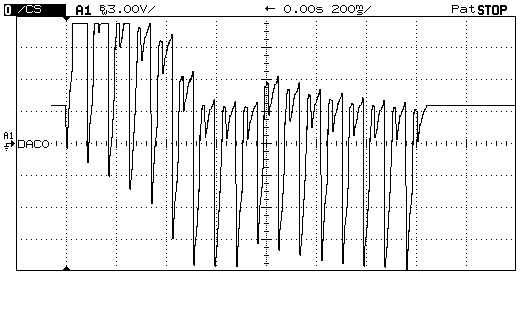

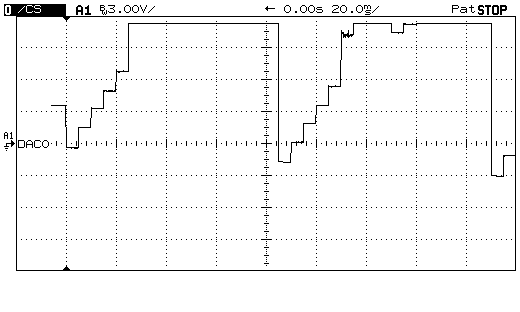

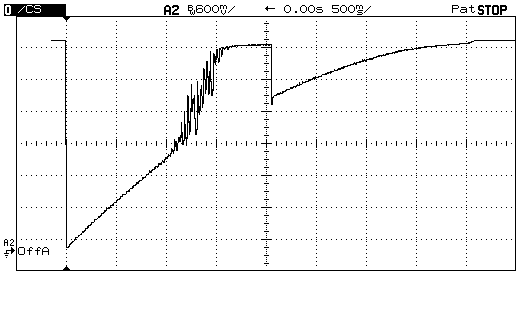

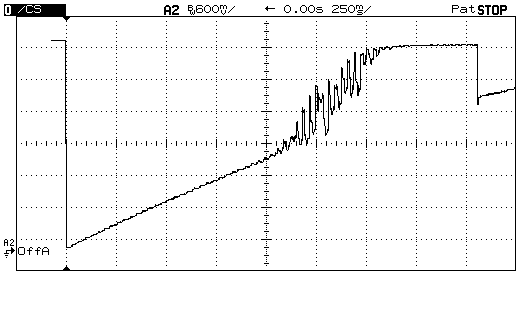

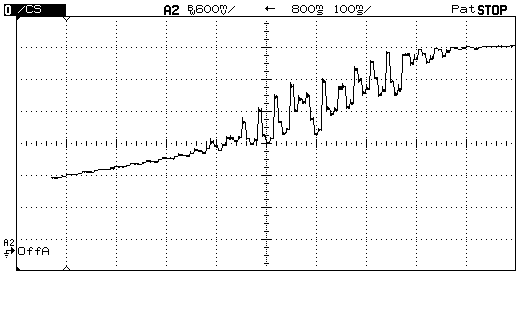

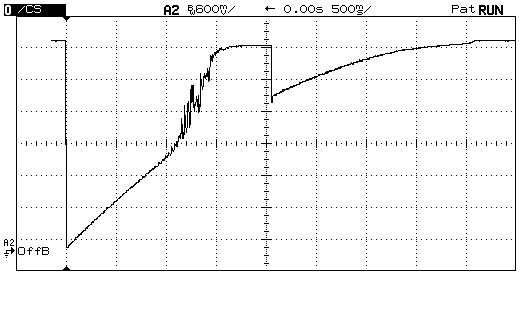

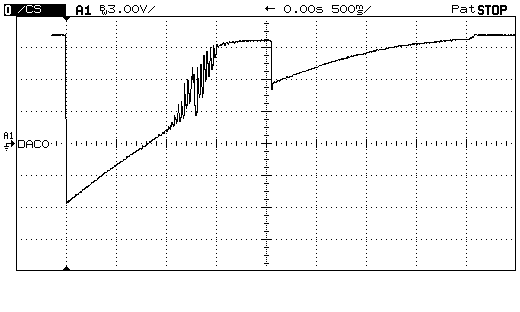

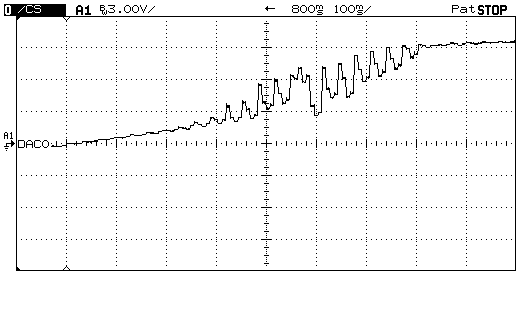

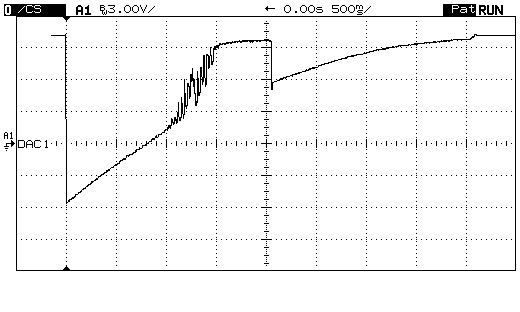

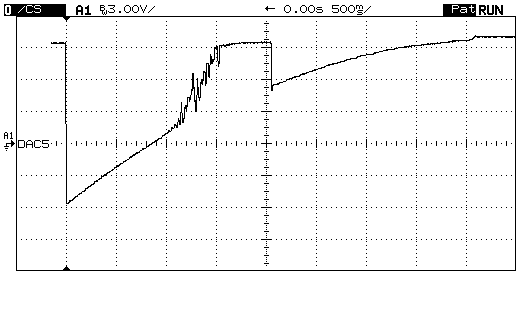

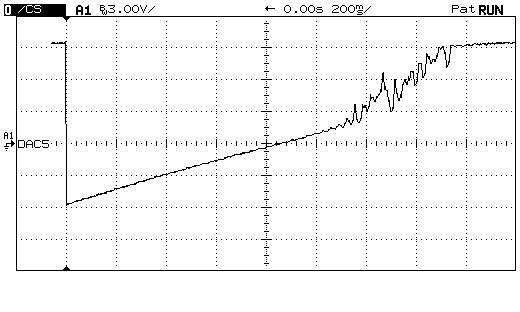

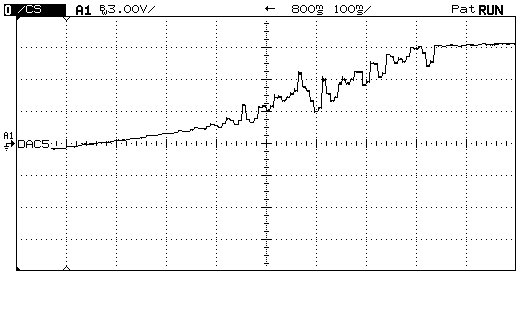

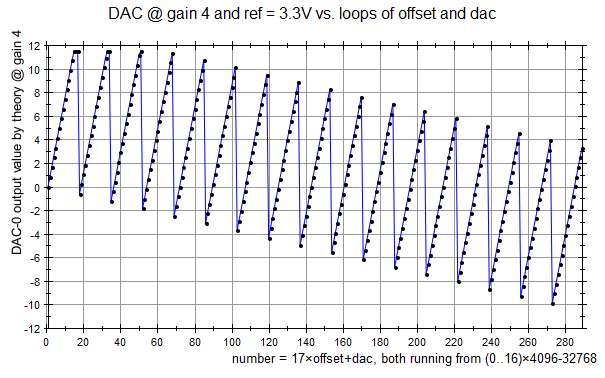

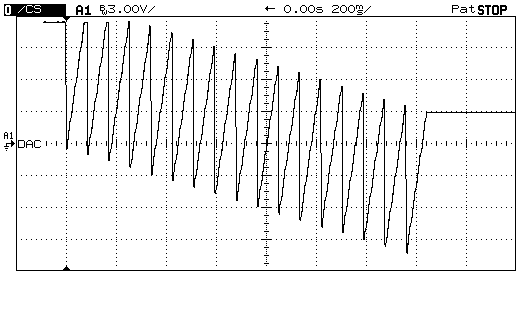

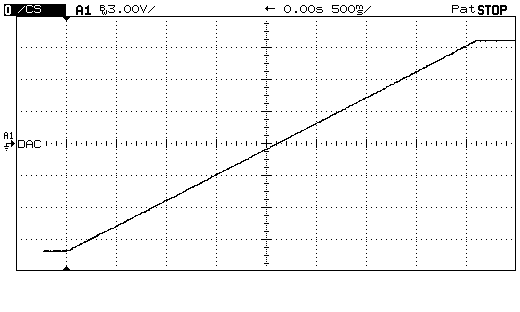

we have a big problem using a DAC8218. Our communication with the device works well. Which we can see at the GPIO handling. We can write and read the registers. But we never get the analogue output which we expect after calculation the formulas.

Are there any erratas for the DAC8218? The youngest data sheet is from December 2009.

Does anyone have experience with the DAC8218 and can give us some advice?

Thanks!

Regards Jan