We are having an issue with the ADC12J2700EVM, where the data from the JESD204B test modes are corrupted at the output of the JESD204B IP interface inside the Arria V FPGA on the TSW14J56EVM board. The ramp test mode is corrupted in the same way as the forum post below:

https://e2e.ti.com/support/data_converters/high_speed_data_converters/f/68/t/466492

The above design uses a Xilinx part but seems to still suffer from the same issue as our design, which is implemented in an Altera part!

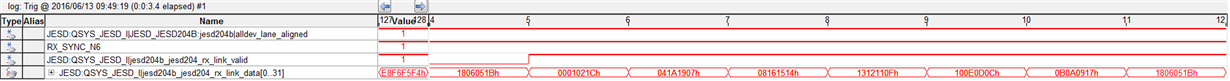

Below is a SignalTap screenshot of the corrupted data for the ramp test:

The initial startup including CGS and ILA operates correctly as observed in the pcs_data register inside the Altera IP block.

The attached text file shows the output from the rx_dataout register of the Altera IP block.

A0A1A2BC A4BAB9A7 A8B6B5B4 B3B2B1AF B0AEADAC ABAAA9B7 B8A6A5BB A3BDBEBF 6061627C 647A7967 68767574 7372716F 706E6D6C 6B6A6977 7866657B 637D7E7F 8081829C 849A9987 88969594 9392918F 908E8D8C 8B8A8997 9886859B 839D9E9F 4041425C 445A5947 48565554 5352514F 504E4D4C 4B4A4957 5846455B 435D5E5F 2021223C 243A3927 28363534 3332312F 302E2D2C 2B2A2937 3826253B 233D3E3F E0E1E2FC E4FAF9E7 E8F6F5F4 F3F2F1EF F0EEEDEC EBEAE9F7 F8E6E5FB E3FDFEFF 0001021C 041A1907 08161514 1312110F 100E0D0C 0B0A0917 1806051B 031D1E1F C0C1C2DC C4DAD9C7 C8D6D5D4 D3D2D1CF D0CECDCC CBCAC9D7 D8C6C5DB C3DDDEDF

We have spent a lot of time on this problem and neither the TI or Altera engineers have been able to explain what is happening.

Is anyone able to explain what is happening and offer a solution?