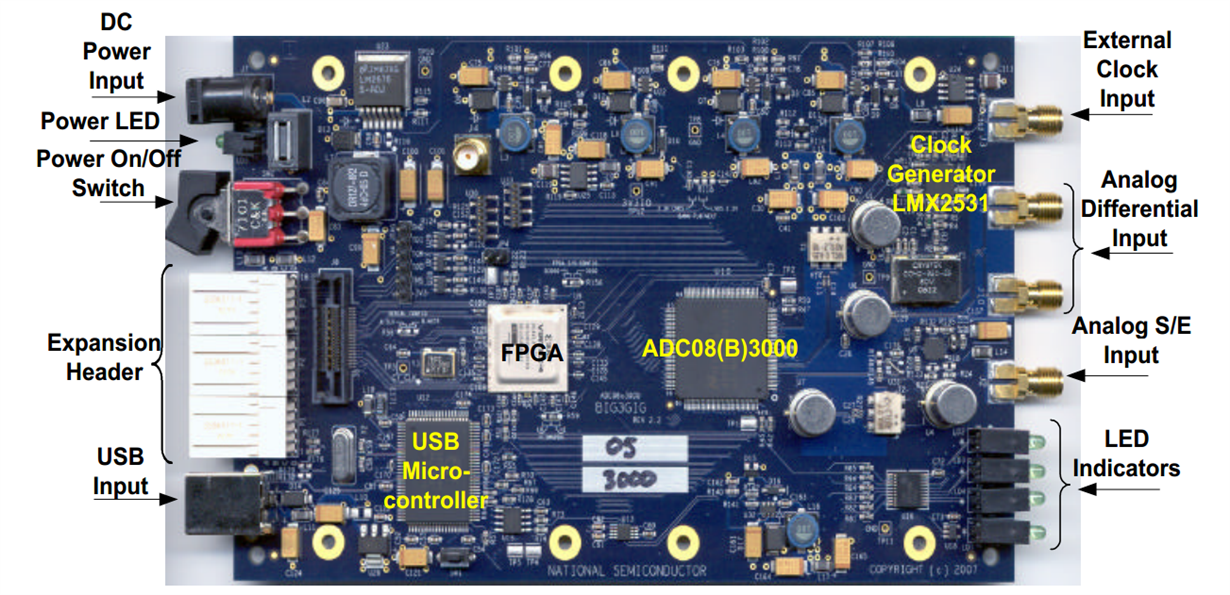

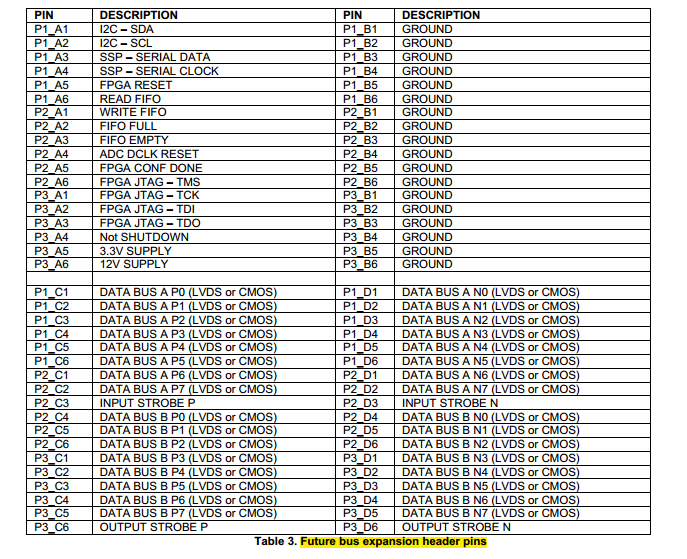

I' m using an Eval board ADC08B3000RB ; But I donnot know if we can get high and low digital levelI (LSB-MSB) from expansion header independently; for example(high and low digital levelI )as follows :

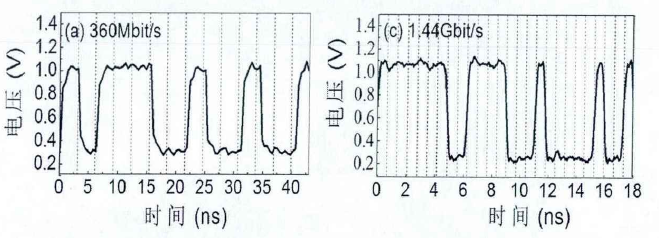

I want to know if we can get connect up with the ADC Eval board expansion header in a way that we can get the LVDS output data onto SMA connectors to connect up to an oscilloscope; In which condition,we can achieve this result.

Best regards,

guoyacekong@163.com