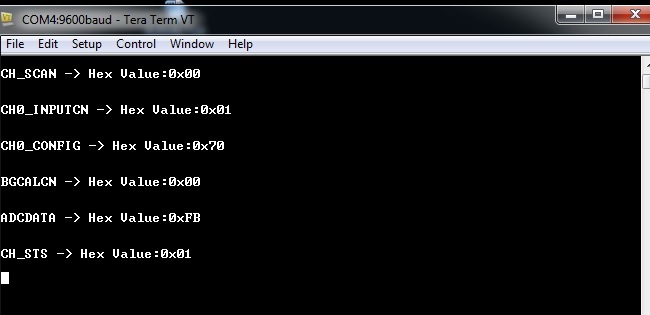

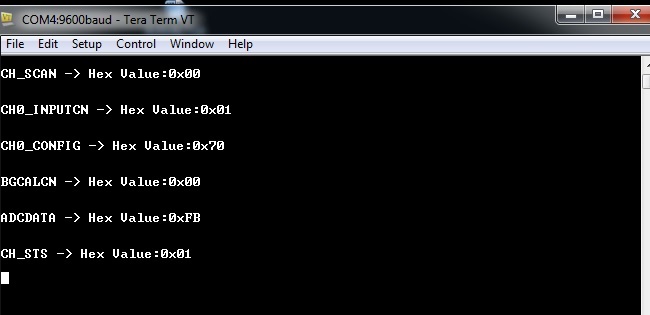

Can I get any reference VHDL/Verilog code for interfacing LMP90098 to FPGA. I do not have any microcontroller on our custom board. i tried to use SPI communication using microblaze softprocessor but could not succeed.

I tried to code myself as per the datasheet but could not succeed.