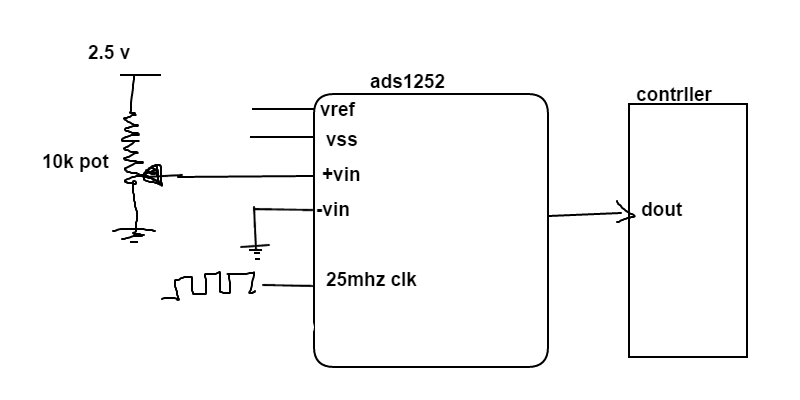

I don't have analog input so i made Potenio meter as variable input,if this circuit is not working I need suggestion,

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.