Hi

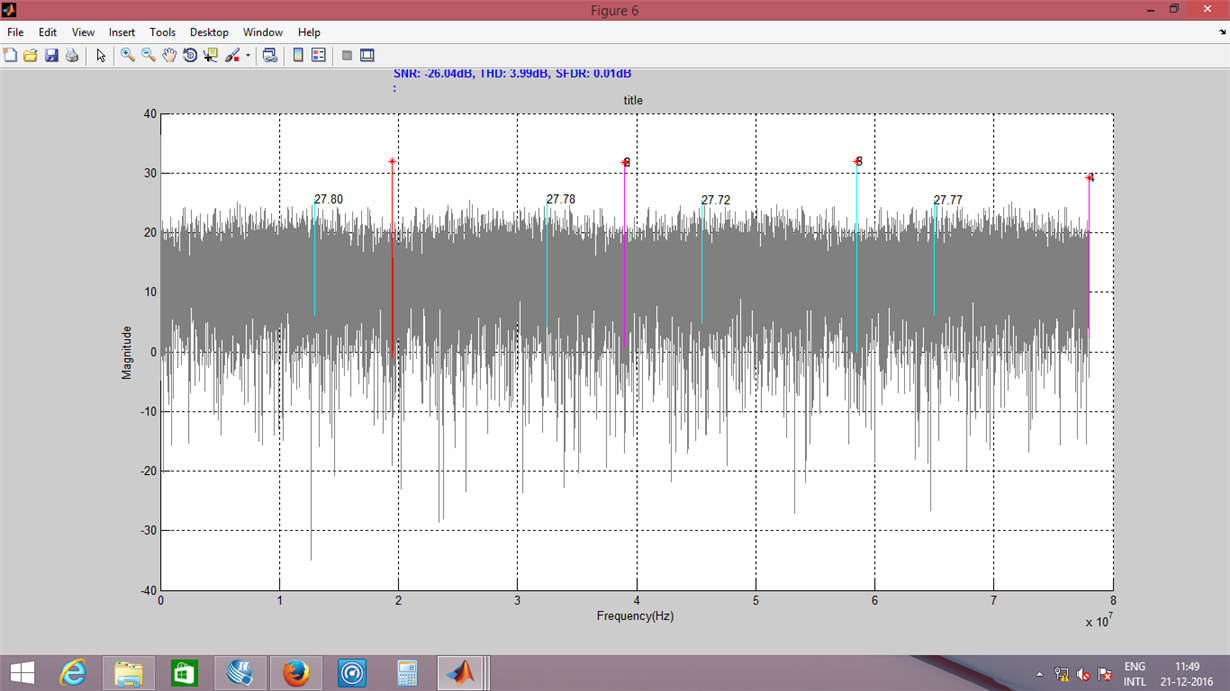

I am using ADC16DV160 in my mixed signal card. The captured ADC data is not clean and has several spikes along with the signal. The spikes are visible even when no IF is fed.

Fig 1 : ADC capture with 36MHz output

Fig2: ADC capture without signal

Why are so many spikes coming at the captured data. Noise level also seems high. What can be done to overcome these issues?