Part Number: ADS1120

Hi

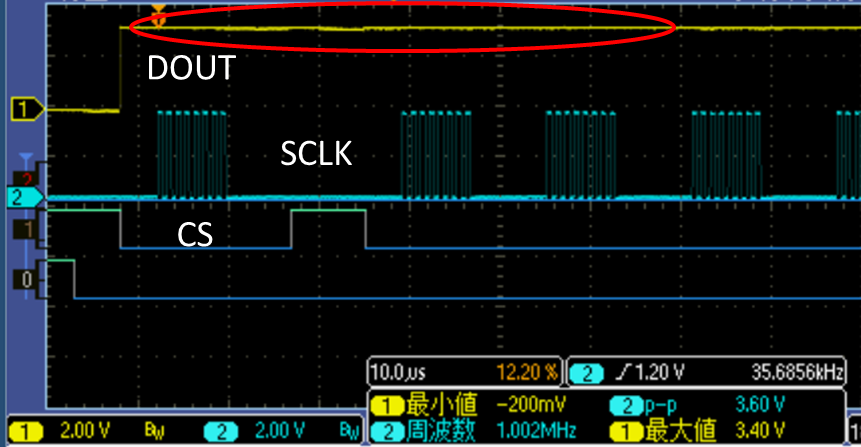

According to the datasheet, DOUT/DRDY is uncertain value after /CS is low.

However, DOUT keeps high after /CS is low in actual like following.

Is it possible to keep it low? We want to make DOUT low until the valid data read.

BestRegards