Other Parts Discussed in Thread: CDCP1803, SN65LVDS100, DAC3162

Dear All,

I have the DAC3162EVM and the Xilinx AC701 (Xilinx Artix7 FPGA Eval Board).

The FMC connector on the DAC3162EVM and the AC701 are perfectly compatible. So I don't have any problems in connecting the two boards.

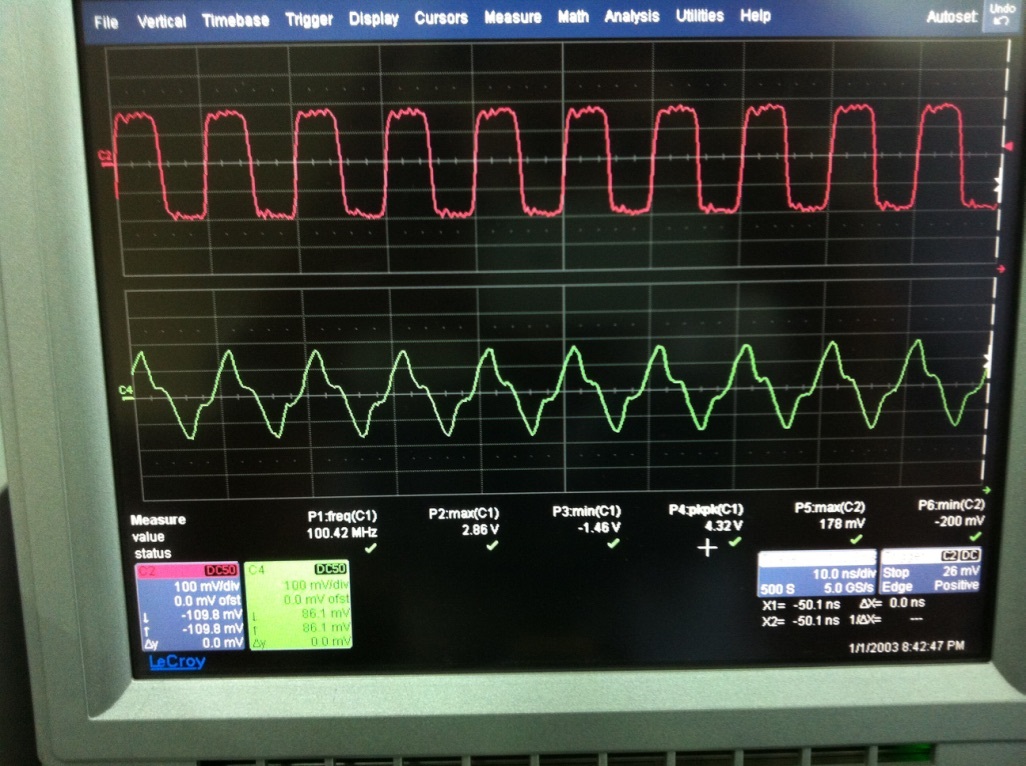

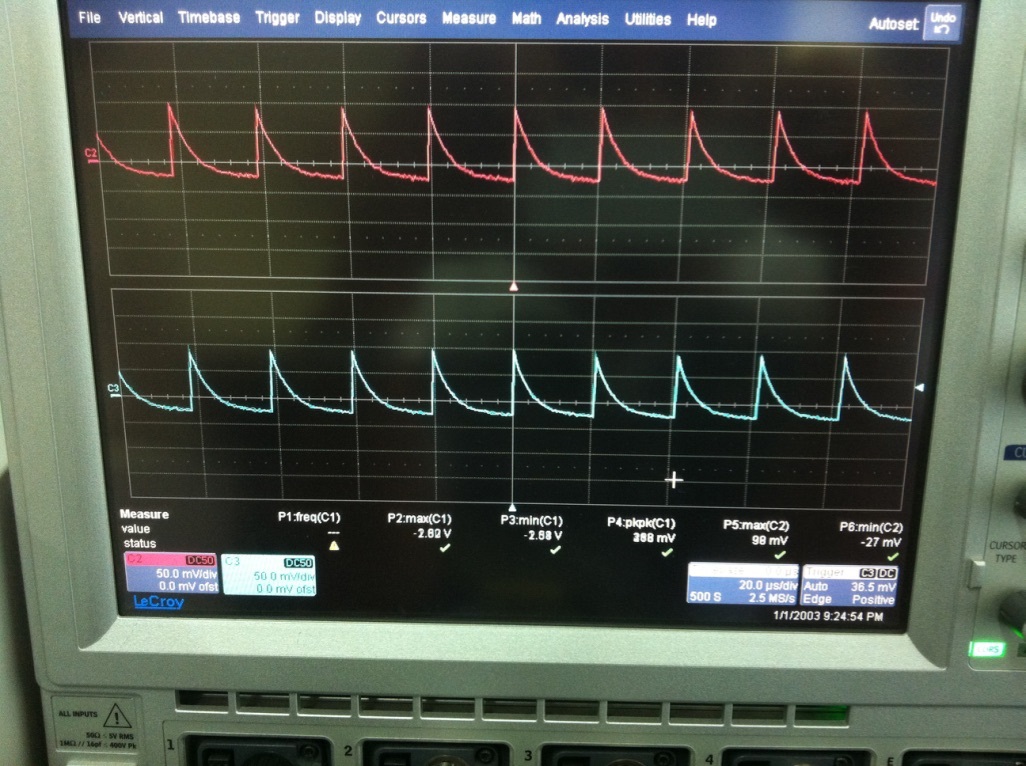

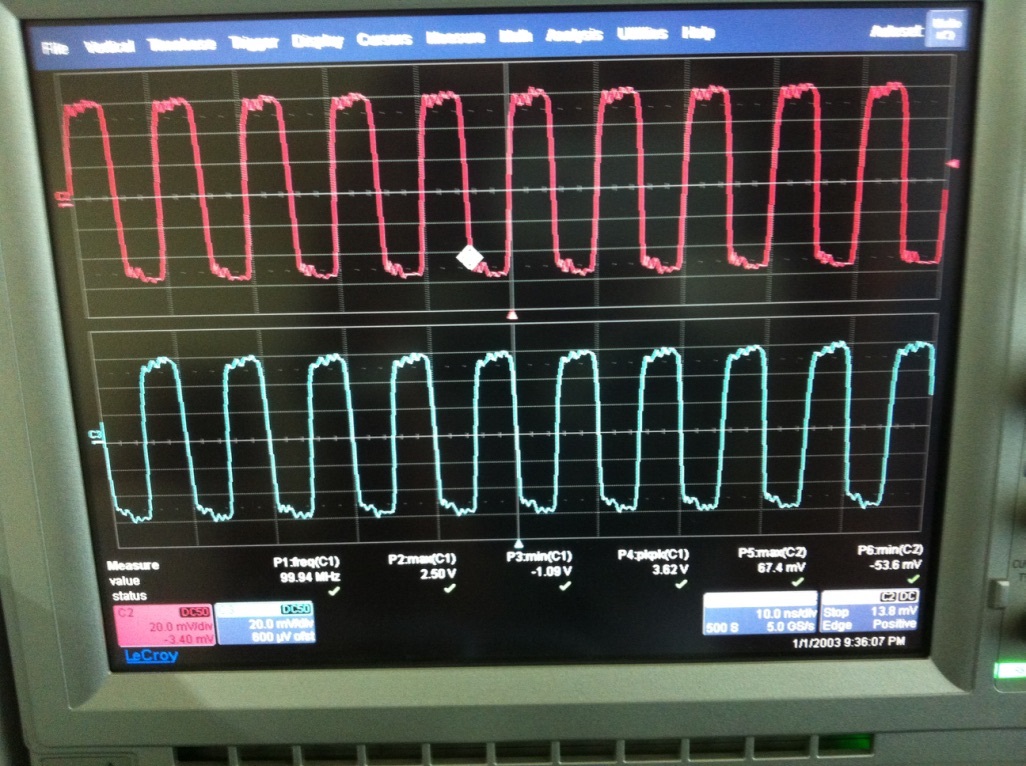

The DAC EVM Board has a TI device CDCP1803 on it. The CDCP1803 takes an external clock signal and provides the DAC Clk, FPGA Clk etc. I am able to give a 200 MHz external clock to the J9 connector of the DAC EVM and also able to tap and see the DAC Clk and FPGA Clk on the Oscilloscope. So far so good.

On the FMC connector of the DAC3162EVM, the FPGA Clk (From the DAC3162EVM board) is LVPECL standard. I have measured the voltages of this clock and found them to be as per the datasheet of the component CDCP1803 (The swing is from 1.5V to 2.5 V for either Clk_P or the Clk_N signals). This FPGA Clk will be the input clk to the FPGA and the DAC Data will be output w.r.t. this Clk. The FPGA Clk and the DAC Clk are set at same rate.

Now, whereas the Xilinx Artix7 FPGA doesn't support the LVPECL standard and the newer Xilinx FPGAs too don't support the LVPECL standard, I want to know which other standard can I select in my FPGA so that it can still take the FPGA Clk (LVPECL) to the Xilinx AC701 Board.

The DAC3162EVM Board has mapped/connected the FPGA Clk to the D19 and C19 pins of the Artix7 FPGA.

Waiting for your suggestion.