Please let me check about DAC5681 required spec for two points below.

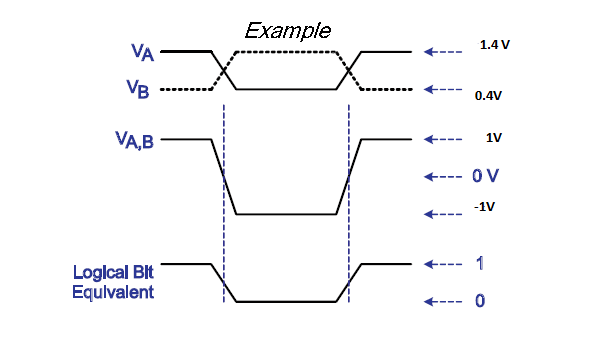

①About CLKIN voltage, datasheet P10 is described 0.4V_min and 1.0V_typ.

Is differential voltage 1.8V, no problem? Is there max voltage?

If 1.8V is problem, is this point bad influence to phase? (please see below background)

②In the datasheet P28, are CLKIN and DCLKP / DCLKN have required timing spec?

I didn't find relationship of CLKIN and DCLK.

If CLKIN and DCLK have large timing gap, is this point bad influence to phase?

【Background】

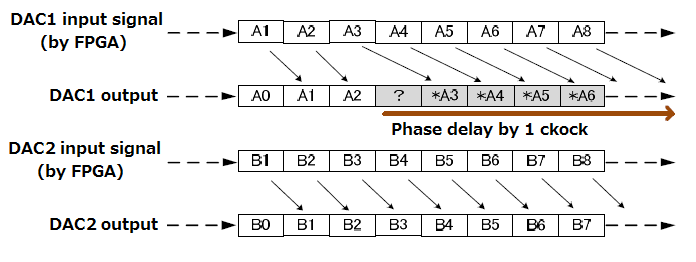

・Customer is evaluating DAC5681 for 3~4pcs parallel connection and require sync phase/timing.

・But very rarely, any DAC5681 is delay the phase for 1-clock timing.

※Image is attached below.

・Customer is inquiring the cause of 1-clock delay and revision point of circuit

Best regards,

Satoshi