Other Parts Discussed in Thread: LMK04828,

Hello!

I have board with FPGA Kintex UltraScale, LMK04828 and ADC12J4000 running at 3 GHz in bypass mode (6Gbps line rate). LMK provides 3 GHz clock to ADC, single 150 MHz clock to Kintex GTH and Sysref signals to ADC and FPGA. JESD core inside FPGA is clocked via GTH.This configuration was checked with EVM+KCU105 and work fine.

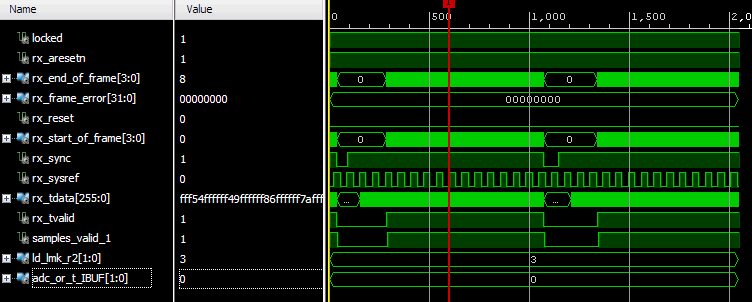

My board successfully pass ILA phase. Some amount of data is received (about 20-30 multiframes and input sine signal is perfect there) and then FPGA drops SYNC to low. JESD core does not indicate any errors at rx_frame_error[] signal. PRBS23 IBER test also pass without any errors and with wide-opened eye.

I tried following with same results:

- change number of frames in multiframe;

- use single Sysref and permanent Sysref clock

- change Sysref phase in the ADC

- enable and disable scrambler

It's look like incorrect control symbols at the end of frames but I have no idea how to fix it

Any other ideas? Thank you.