Hi,

I'm new to these EVMs. I have ADS4149EVM Rev B, TSW1405EVM Rev C, and the GUI HSDC Pro v4.70. I followed the ADS4149EVM setup instructions as best I could (it shows the TSW1200 and its 2p0 BETA, not the TSW140x or HSDC Pro v4.70). Please help me with getting started.

ADS4149EVM jumpers are as in Table 1 (no amplifiers). 3.3V (50mA) to J16/J12 for on-board voltage regulators. USBs from PC to each 'EVM. One GUI window on PC.

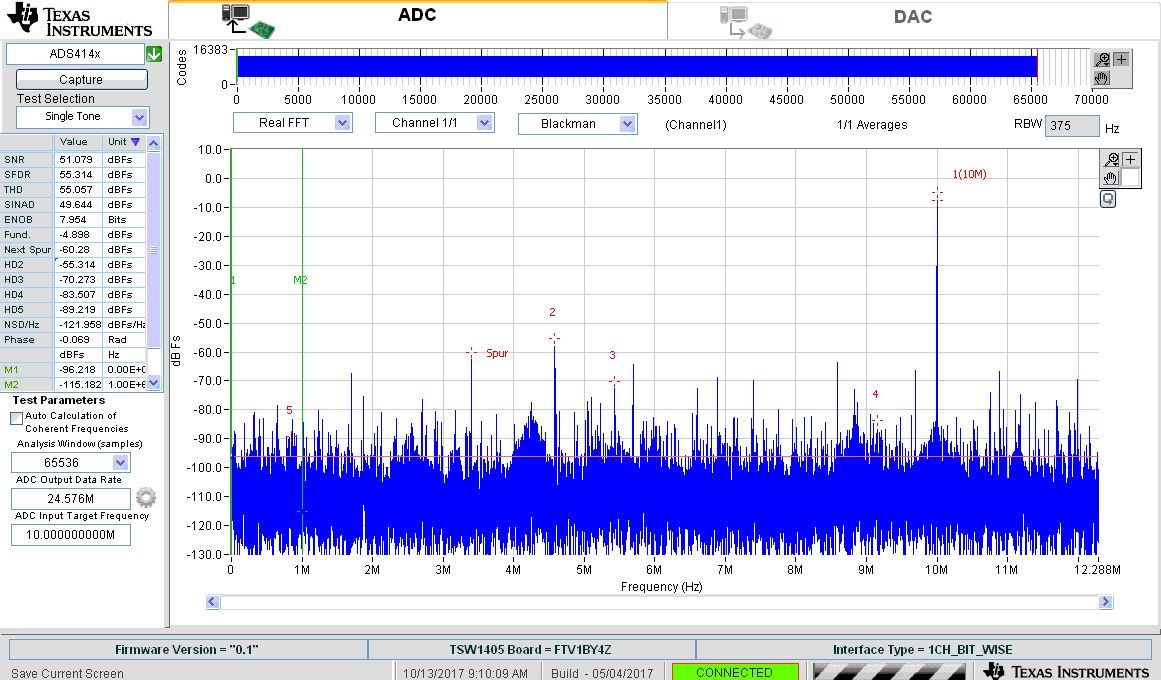

Clock = 24.576 MHz sine, 1.5Vpp 0V offset.

Ain = 10 MHz sine, 1.3Vpp 0V offset.

GUI lower left = test parameters:

samples = 64k

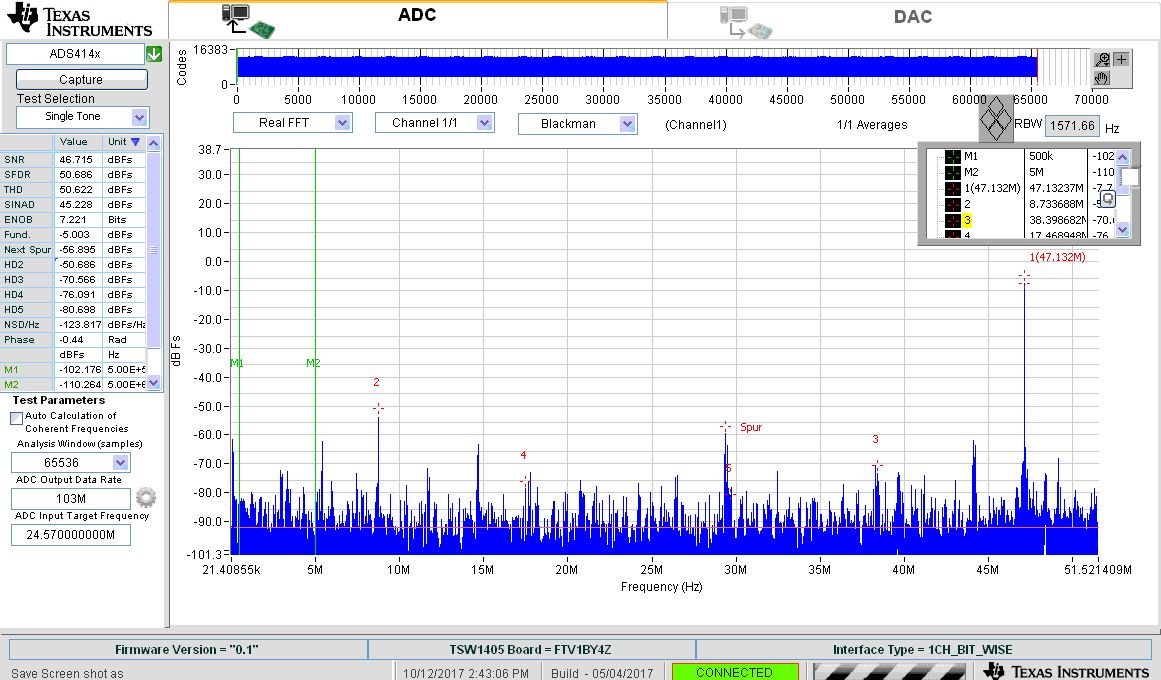

ADC output data rate =103M

ADC input Target freq = 10M

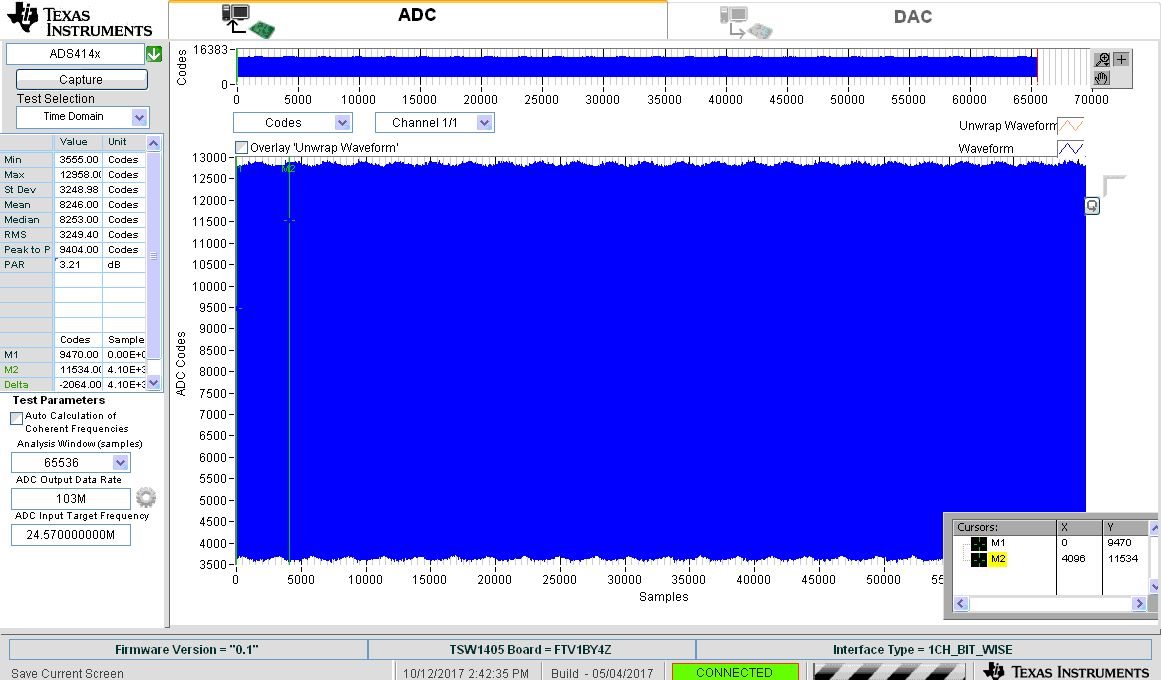

Downloaded Firmware to '1405 and the '1405's LED is ON. When the Ain is off, the "Capture" codes = 8,242 to 8,251 (8,192 is ~ideal? Vcm=0.9648V), "Real FFT" shows f1=113k at -113dBFs. These seem OK.

When Ain=ON, the "Capture", the codes range from 4,237 to 12,266 (seems OK). However, the "Real FFT" (Blackman) shows nothing at 12.576MHz (f1=42M, F2=19M, f3=22.7M, f4=38M, f5=3.6M)

Why nothing at 24.576MHz? Am I doing something wrong with voltages, frequencies, or settings?