Other Parts Discussed in Thread: CDCE72010,

Hi,

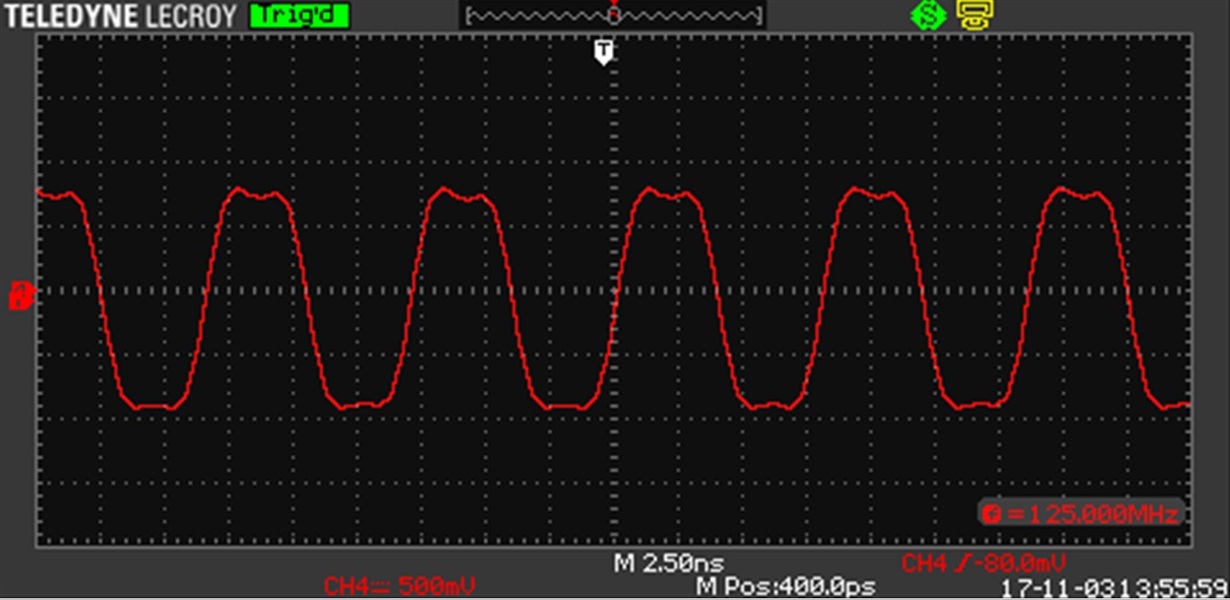

We have DAC5682Z DAC on FMC interfaced to Virtex 6 FPGA and CDCE72010 for input clock. I have been using it at 250 MSps for generating waveforms without any problem for a few years. But when I tried higher sampling rates I got some bizarre results. I conducted tests at 500 MSps and 1 GSps and here is what I observed:

|

Main Clock(MHz) |

Data Clock(MHz) | Data Waveform*(MHz) | DAC Output(MHz) | Expected DAC output(MHz) |

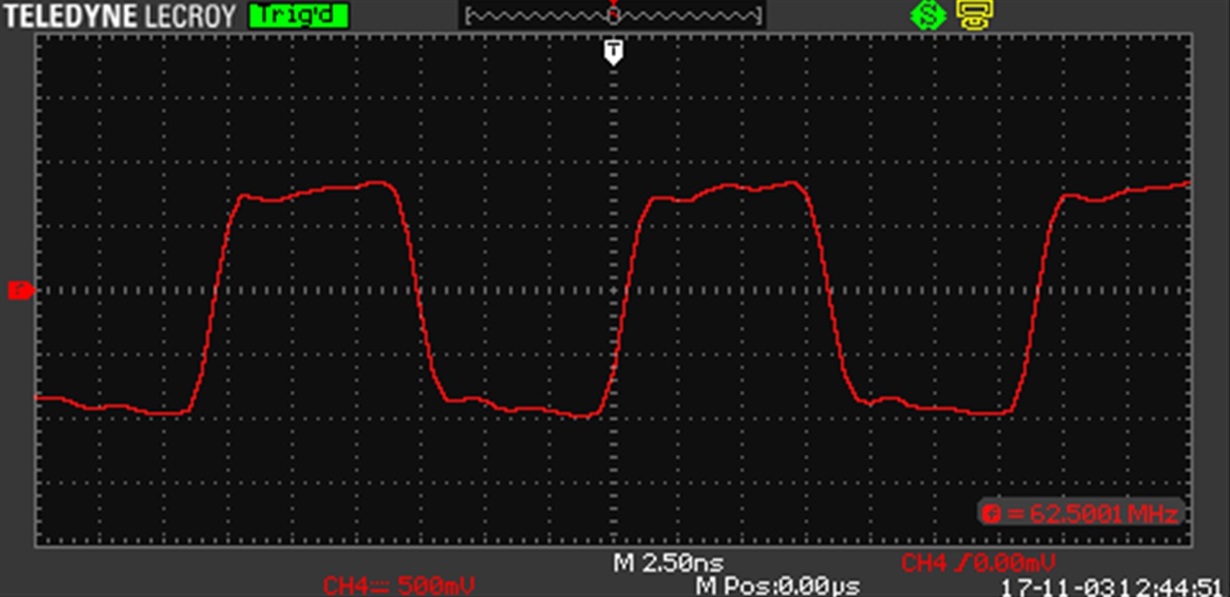

| 250 | 125 | 125 | 125 | 125 |

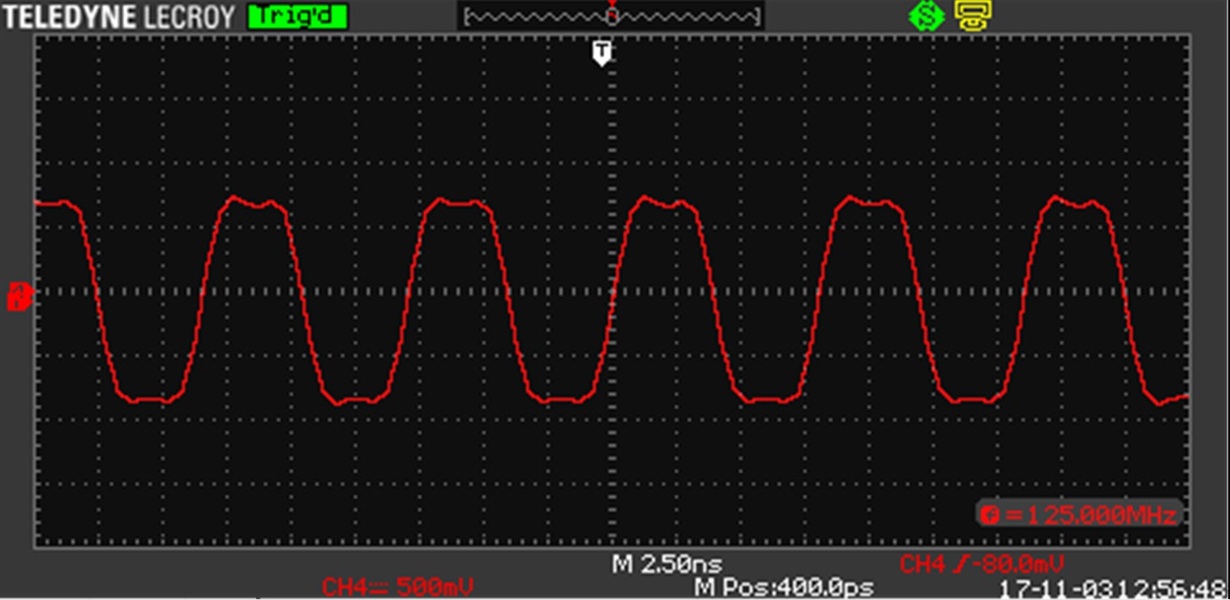

| 500 | 250 | 250 | 125 | 250 |

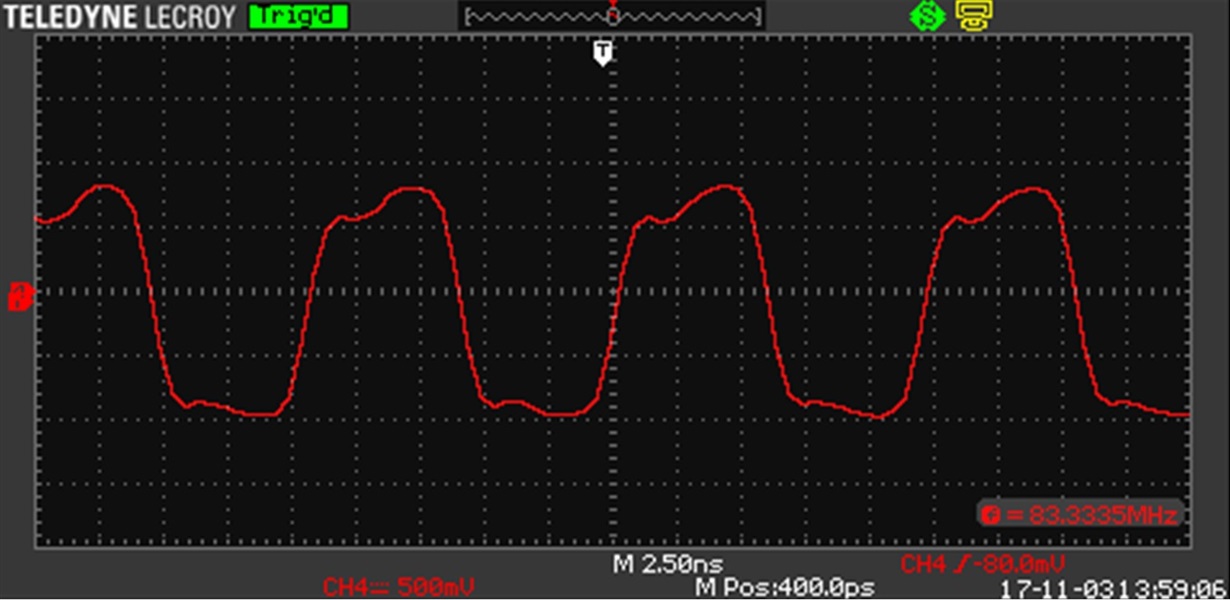

| 500 | 250 | 125 | 62.5 | 125 |

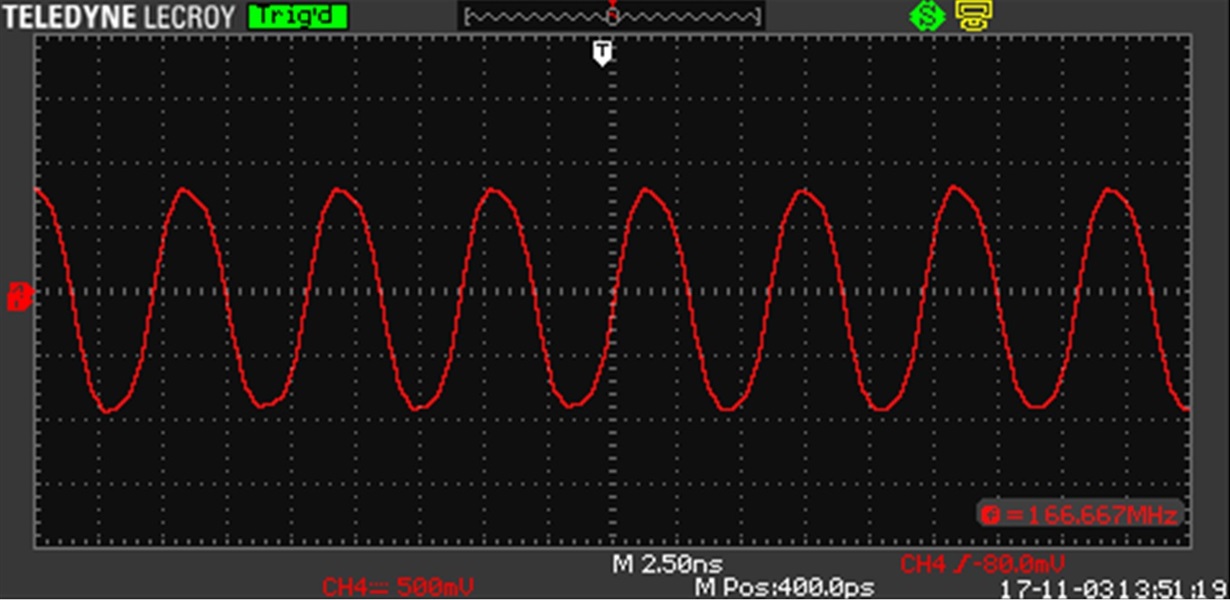

| 1000 | 500 | 500 | 166.667 | 500 |

*data waveform is alternating extremes.

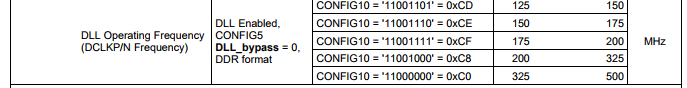

I have turned off interpolation filters and PLL and am setting config 10 for DLL as per table 7.7 in data sheet. I am also sending appropriate sync event after every 125M cycles,

I thing I am missing something very trivial that is resulting in these weird factors of 2 and 3, and would appreciate any help in resolving this.

Thanks in Advance.

Regards,

Arpit.