Other Parts Discussed in Thread: DAC3484, THS3217

Hello,

My customer is using DAC3162 (500Msps) and faced with below issue. Please help to get answer asap. They hope to get answer by tomorrow due to PCB OUT schedule.

In their system, ‘LVDS Lcoslk 120MHz’ in attached block diagram is shared by DAC3162 and LCOS display.

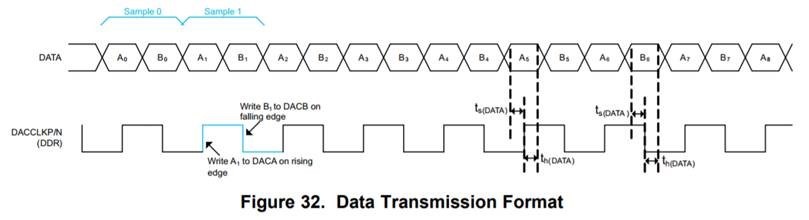

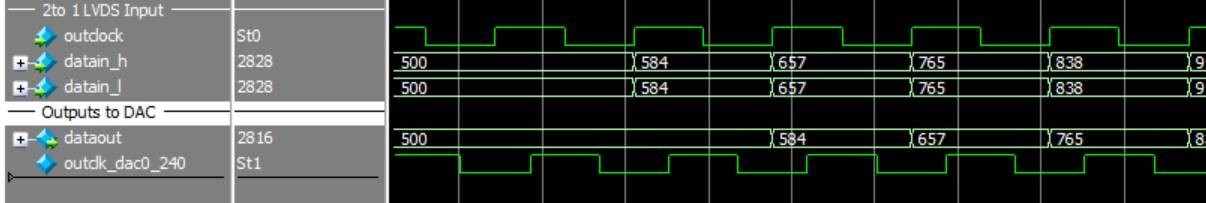

And the LCOS panel needs to get aligned analog output signal ‘DACA’ and ‘DACB’ of DAC3162 to get clear image (1080p 120fps), but the output image is distorted by output of DAC3162 due to delay between processing time of DATA A and B as described in Figure 32 as below capture.

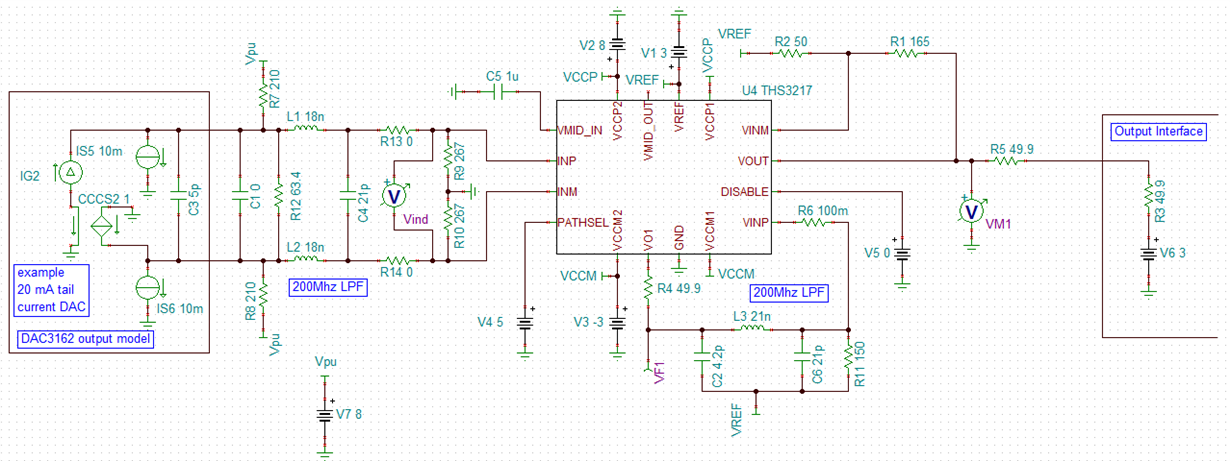

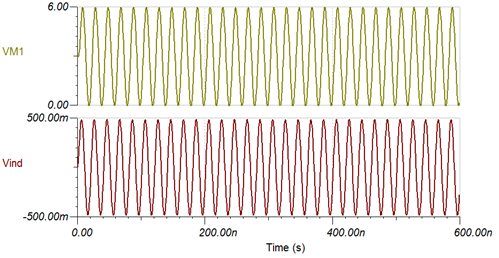

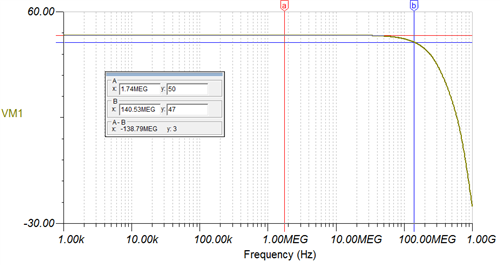

Another issue is that output range of IOUTP and IOUTN is too low about 0.5V. LCOS panel needs to get 0V to 6V peak to peak. So they are using external OPAMP (MAX228) to amply output about 12 times of DAC. They hope to get answer how to increase output level of DAC3162 and application note to get 0V to 6V analog output.

They also hope to get suggestion for 1Gsps Dual-Channel DAC if this issue can be solved.

1. We are using two channel output DAC3162. We just noticed that analog output port A and B has half clock phase off.

For our application, the output of port A and B should be aligned.

Please let us be advised how we can resolve this issue.

2. The output range of DAC3162 is 0.5Vpp with DC offset voltage.

We need to amplify the DAC output signal from 0.5Vpp to 6Vpp of 0V to 6V swing with 3V bias voltage.

Could you any suggestion of application circuits for getting the 6Vpp?

Best regards,

Shaka Lee