Other Parts Discussed in Thread: REF6050

Hi all,

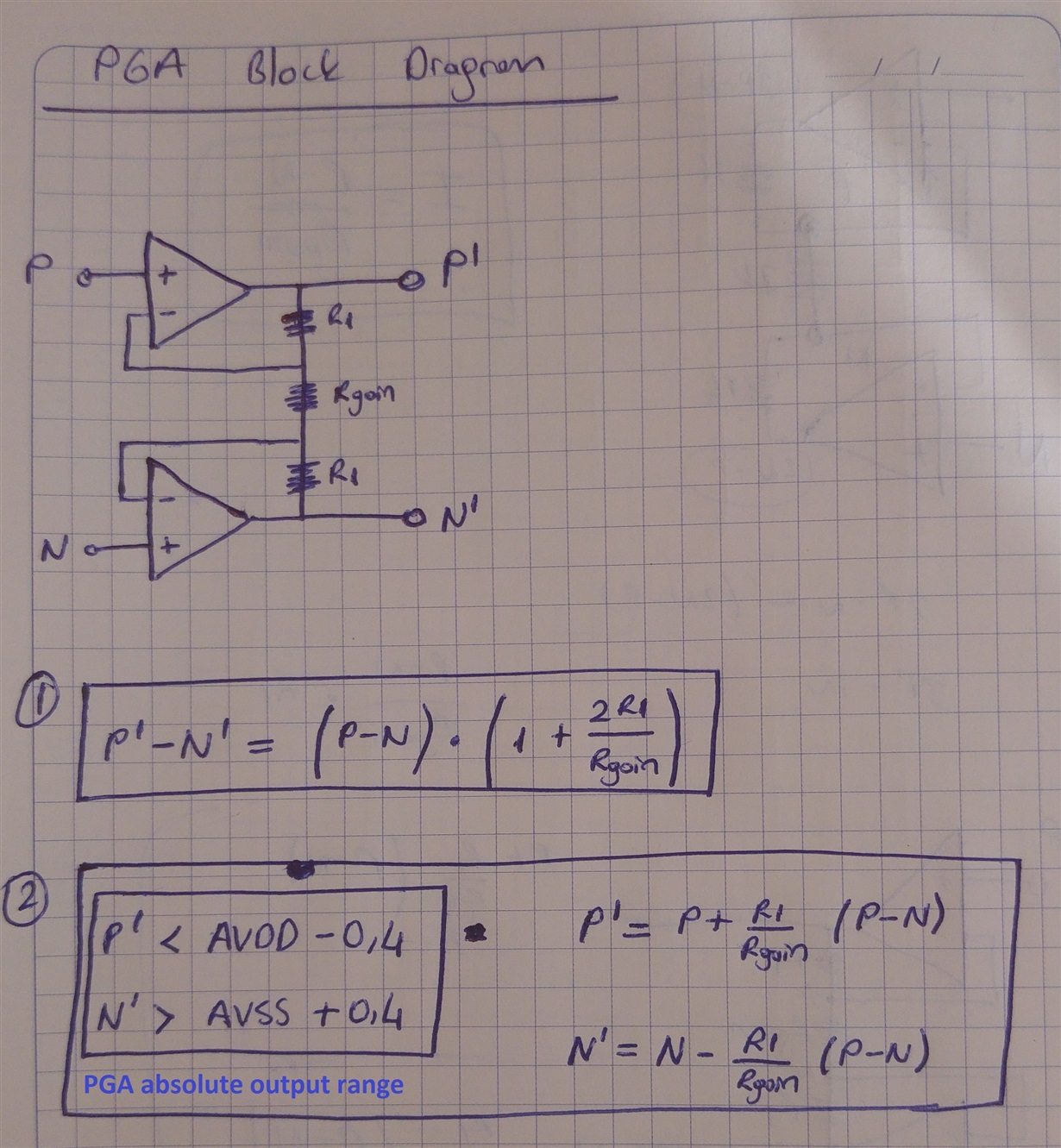

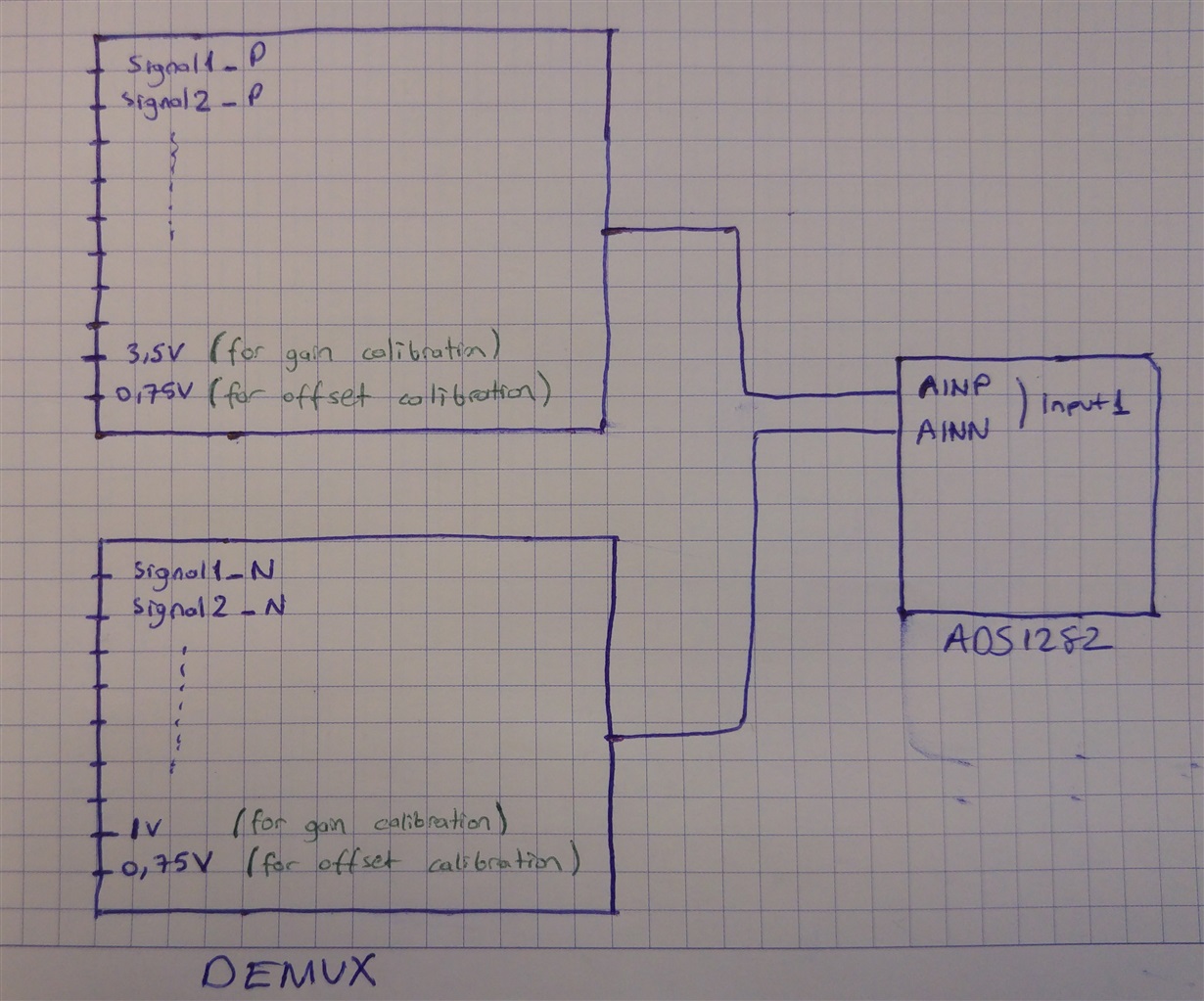

I have some questions about PGA block diagram in ADS1282 datasheet. As i understood from the datasheet, there is following circuit in the ADC. Am i right?

If i think wrong, please share correct PGA circuit. According to correct PGA circuit, i will adjust analog inputs or adjust gain for appropriate PGA output range.

Regards,

Eren