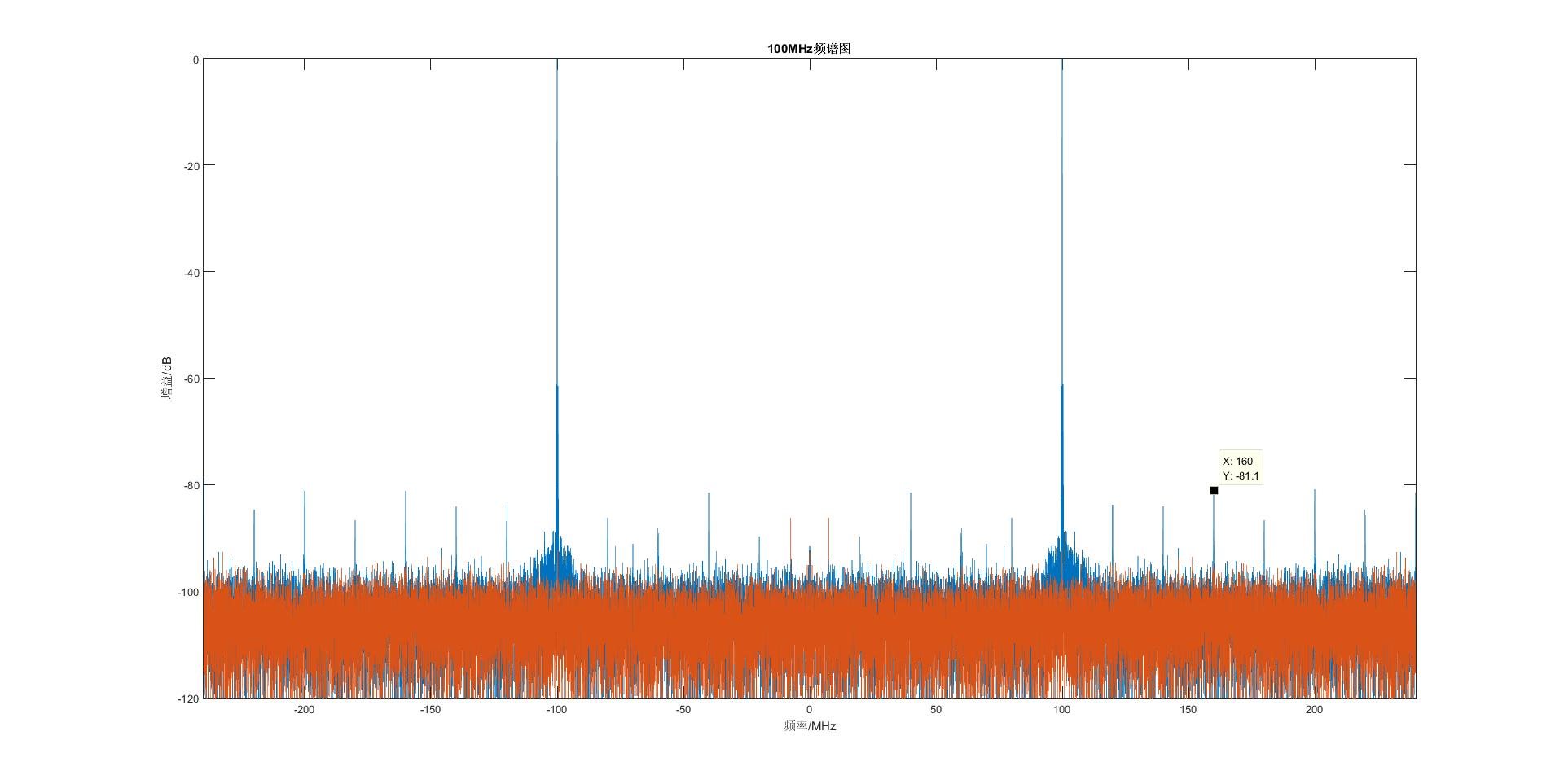

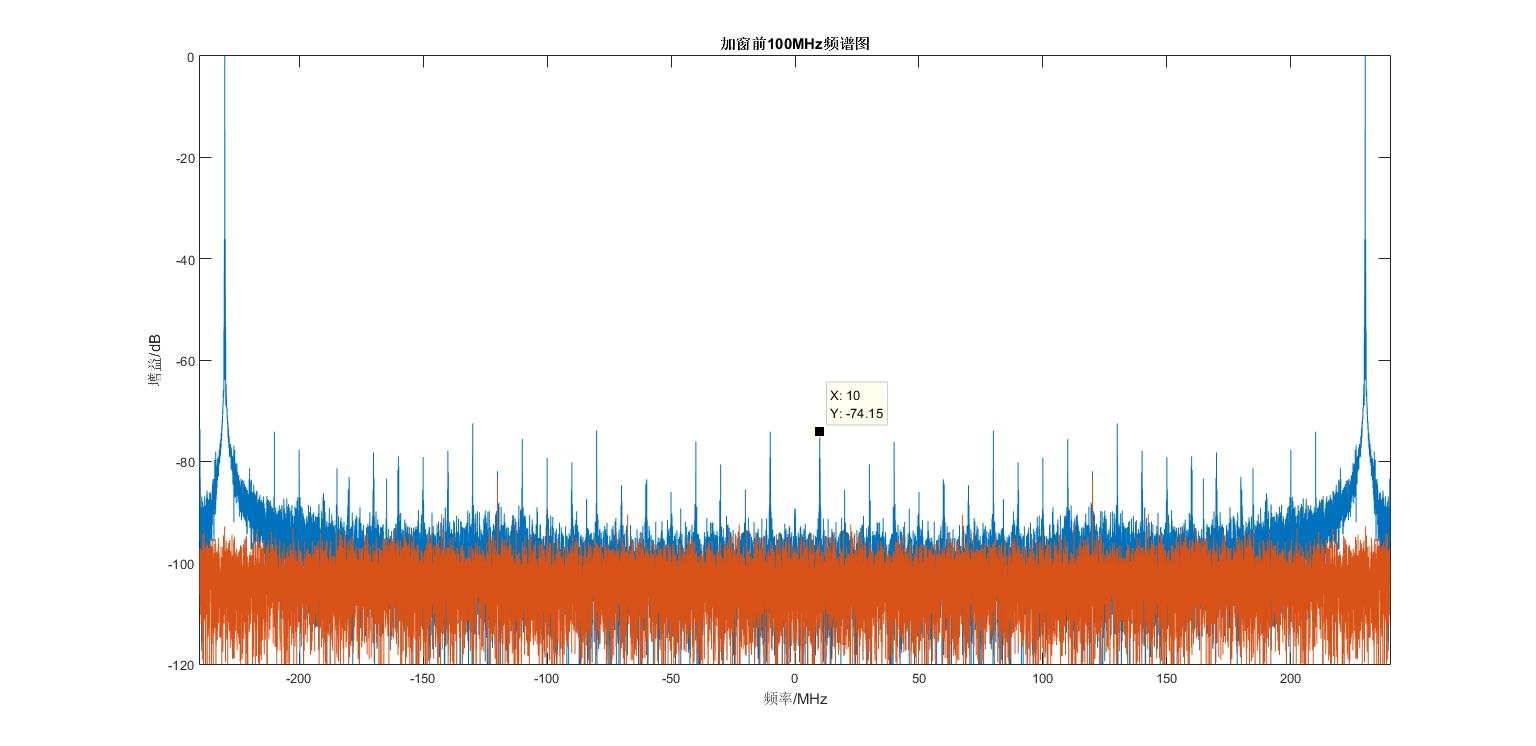

I test the SFDR of ADS54J54 on my own sample PCB board. The sample rate is 480Mhz, and the frequency of the input sine waveform are 10MHz, 100MHz and 230MHz. The SFDR of 10MHz is okey. But there are many spur component when the frequency are 100MHz and 230MHz. And the location of the spur between -fs/2~fs/2 are (M*Fs-/+ N*fin) . I think these spur are folded from the other nyquist feild. But I don't know why.

I take some notice into account as follows when I test the ADS54J54.

1. I insert a bandpass filter in the analog input of the ADS54J54. Central freq = 100MHz/230MHz. BW = 10MHz. The restrain at HD2 and HD3 are greater than 60dB. The amplitude of higher-order harmonic measured through spectrum analyzer are very small. So I don't think the spur come from the input sinewave.

2. I power down LMK04828B's SYSREF output after the JESD204B established.

3. I sample the noise of the PCB board , there are no other coupling freqency signal.

Now the SFDR of 100MHz is a little better but not perfect, SFDR=81.1dB. The SFDR of 230MHz is terrible. SFDR = 74.15. I realy don't konw where the spur comes from.