Other Parts Discussed in Thread: OPA2836, OPA2301, OPA2365

Hi all

Would you mind if we ask ADS7865?

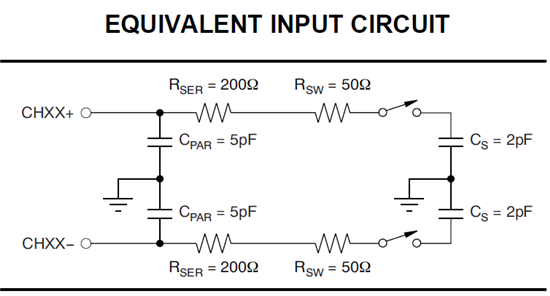

How much is the internal parasitic capacitance?

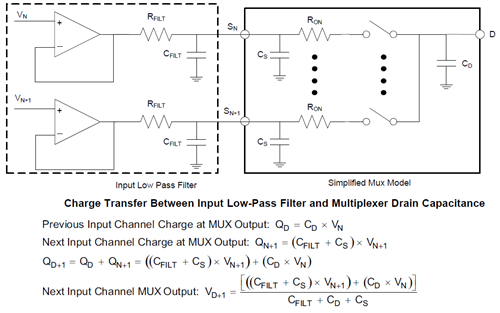

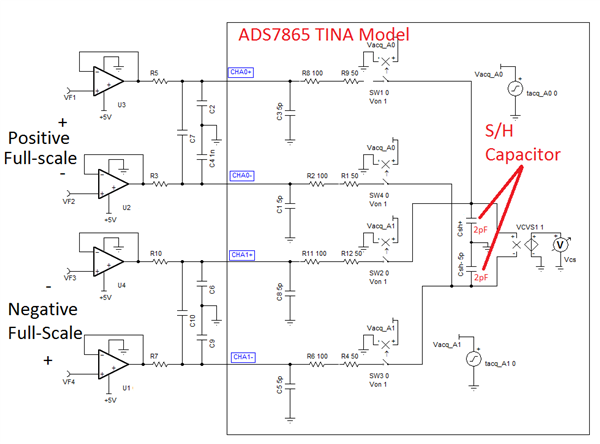

Our customer is worried about memory effect by changing channel at MUX.

In order to prevent from memory effect, if you have some advice, could you let us know it?

Kind regards,

Hirotaka Matsumoto