Other Parts Discussed in Thread: ADS6444

Team,

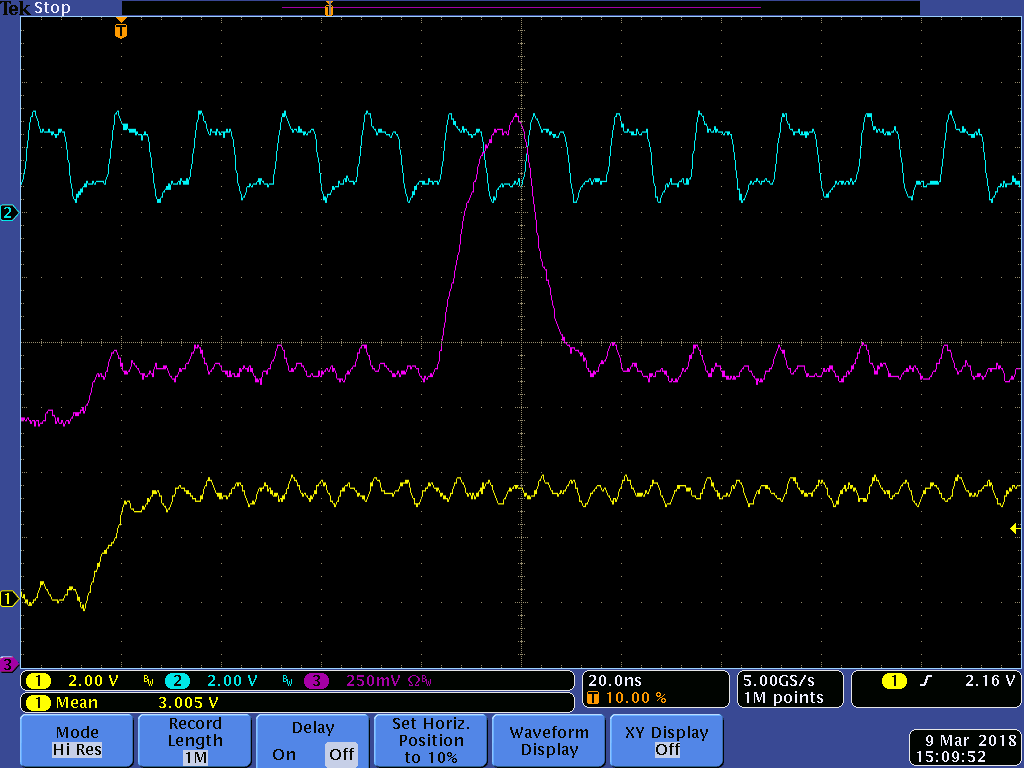

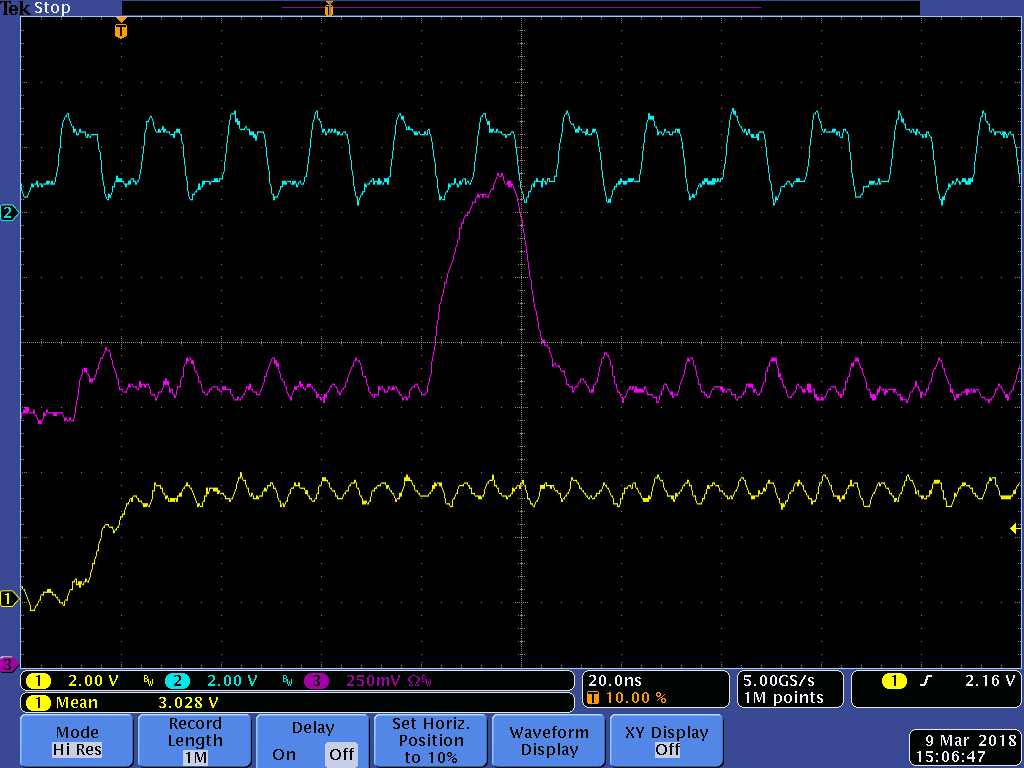

During the bring up of a custom system the digitalized output of the ADC3443 is not as expected, for a given analog input.

Could you please confirm if the sampling is done on the rising and falling of the Input Clock?

Fig 141 of SBAS670B tells that the sampling is done on the falling edge. Is it correct?

http://www.ti.com/product/ADC3443/datasheet/parameter-measurement-information#SBAS6703708

What is the settling time/delay on the analog input signal?

Thanks in advance for your help.

Anthony