Other Parts Discussed in Thread: LMH6703, LMH6702

Hello TI,

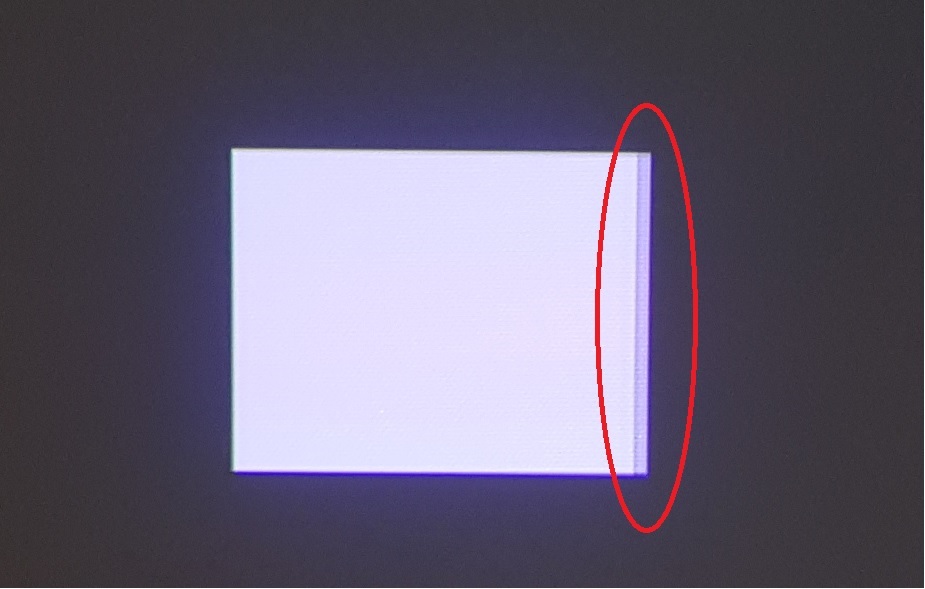

My customer developed display equipment and they found there is a ghost issue on Video output as below picture. You can see the adding line on right side of rectangle in Red circle. And they suspect this issue came from Delay of data.

Video Pass: PC -> (HDMI) -> FPGA (12-bit parallel input) -> DAC5662A -> OPAMP (MAX4304) - > Panel

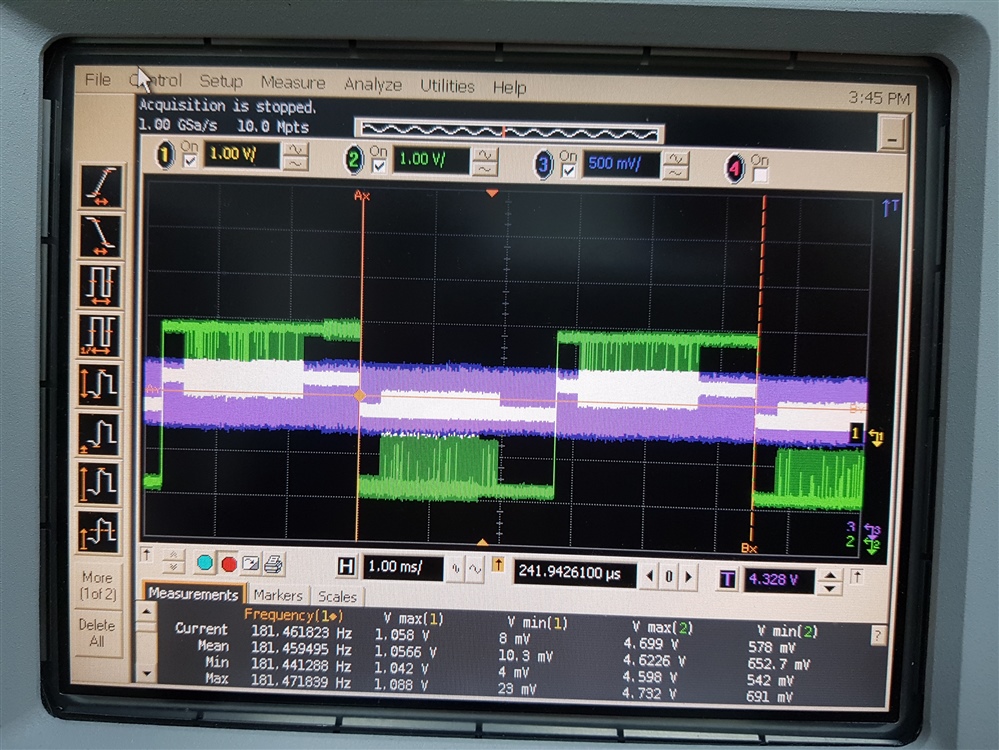

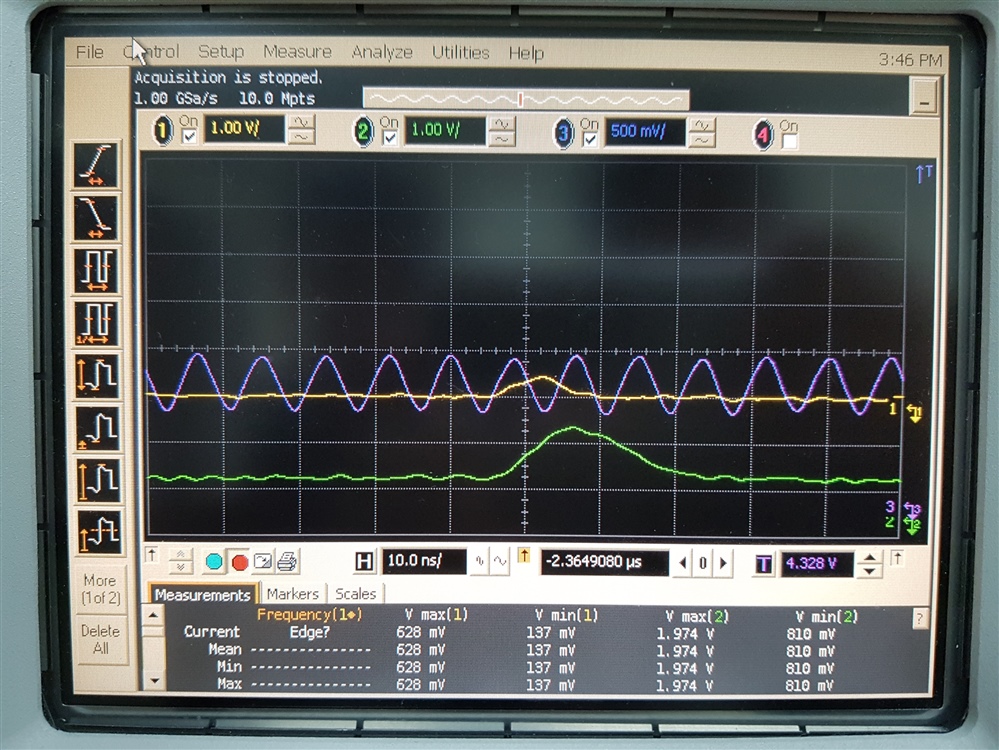

Please take a look below captures. MAX4304 amplifies 10x and it makes more delay compare to DAC output.

- Question1. Is Yellow line (IOUTA1 of DAC5662A) in spec as datasheet of DAC5662A? The IOUTA1 should be the same as Input Clock which is 120MHz and the period is 8.3nsec. As the capture in below, the output of DAC5662A has about 12nsec period which is more than my expectation. Is there a way to reduce period of IOUTA1 by reducing timing of rising edge and falling edge?

- Question2. Please help to review attached schematic (DAC + OPAMP) and recommend faster TI’s OPAMP than MAX4304. It seems MAX4304 makes about 10nsec delay in datasheet.

Yellow: IOUTA1 of DAC5662A

Green: LCOS_VID2 for Display Panel (MAX4304 output)

Magenta: 120MHz Clock IN for Display Panel

Best regards,

Shaka