Other Parts Discussed in Thread: DAC38RF80

Hi all,

We have a question regarding configuration of the DAC38RF80 on the TSW40RF80EVM RF evaluation board interfacing to a Xilinx ZCU102 evaluation board. We are using this device combination in a development project. Interface from the Xilinx evaluation board uses a single GTH transceiver and an MTI JESD-204B IP core.

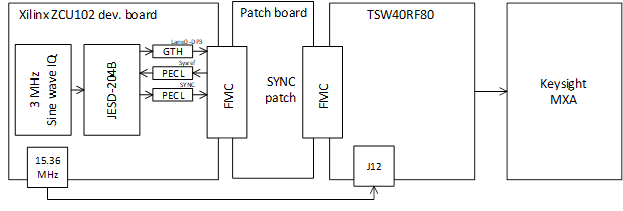

Schematic of our test setup is as follows:

Configuration of the TSW40RF80EVM board is done via the TSW40RF80EVM GUI application.

We are successful configuring the RF board for 7.3727 Gbps lane rate (JESD Mode 12410) with SYNC request disabled for “Link Configuration Error”. This mode does not use the DAC PLL. However, this mode is not compatible with our application requiring a sample rate of 245.76 MSPS, and we would therefore like to change to 9.8304 MHz lane rate (JESD Mode 12410, with use of the DAC PLL), but are not able to configure this mode to provide proper output. (Please note that we can send pictures of the spectrum in private message along with the GUI screen dumps of the different fans showing the used TSW40RF80EVM board configuration and active alarms, also a Vivado ILA dump showing JESD signaling at the output of the JESD-204B core in the Xilinx FPGA).

Note also, that we have successfully tested the high speed links from the Xilinx board to the TSW40RF80 using PRBS7 test patterns. We therefore expect that signal integrity problems are ruled out.

We have spent extensive time trying to correct the configuration. We would therefore highly appreciate if you can help with guidance on obtaining the correct configuration.

Best regards

Ghafoor