Hello,

I would like you to confirm about below.

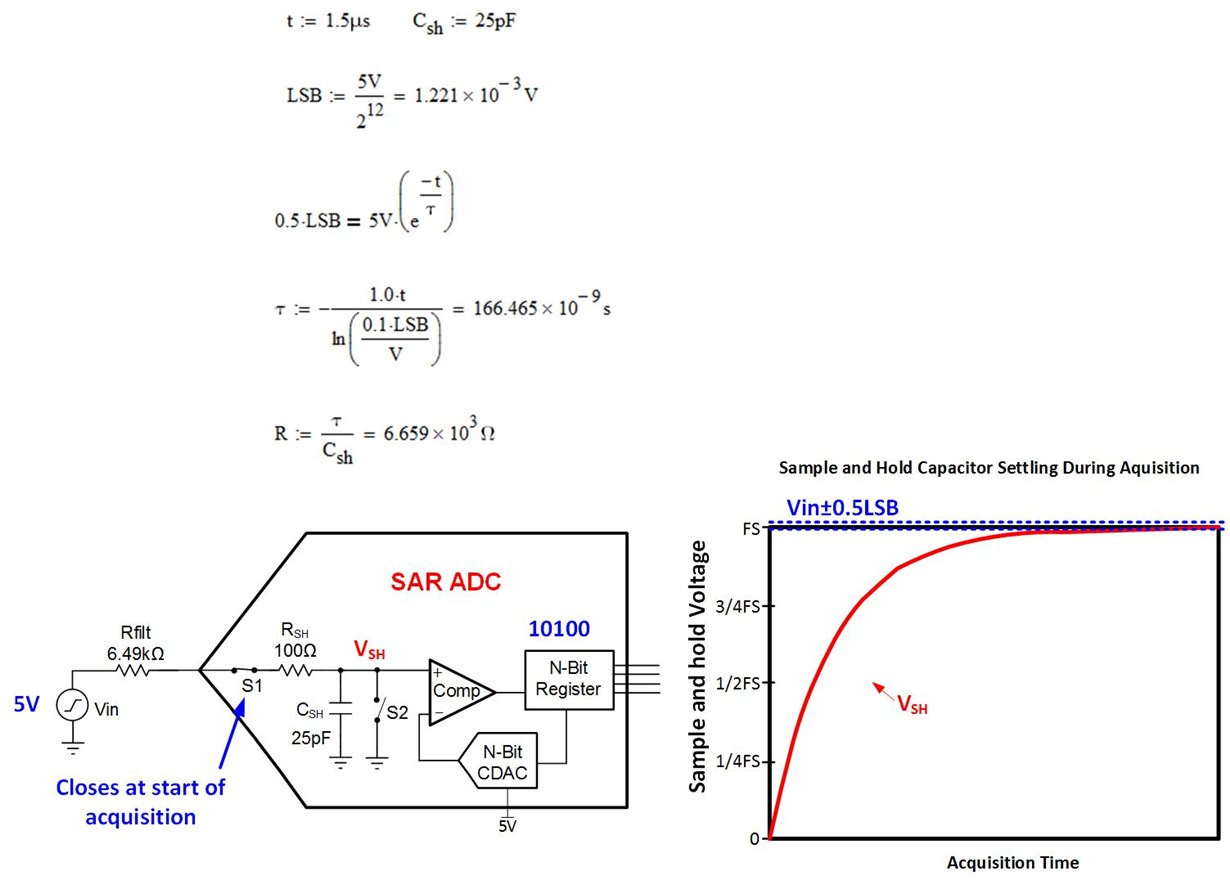

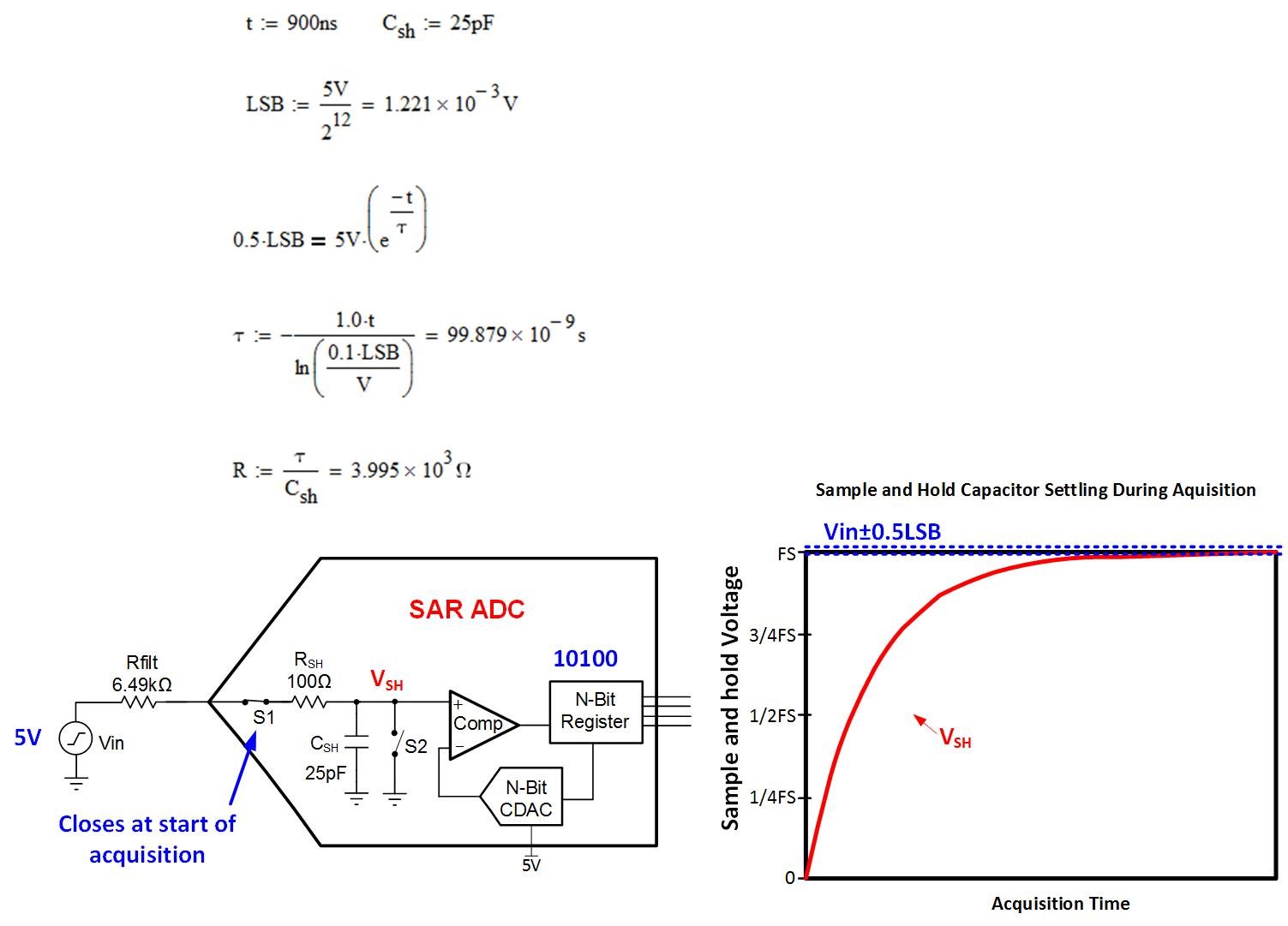

* Could you please tell us allowable source(input) impedance ?

We would like to input voltage which is devided by resistor to CHx.

However, there is no spec about source impedance. So, we are not sure how many resistor value should be allowable.

Best Regards,