Other Parts Discussed in Thread: TMS320F28379D

Dear all,

I am still having problems to use SPI with the ADS8694.

If I use GPIOs without the SPI, the ADC responds to all my commands and sends results back. All the signals are there as they should.

However, if I use the same pins under SPI, I can only get the buffer full of 1's

I control the SPISTE signal separately, and I am by now not using DMA.

If I choice SpiaRegs.SPICCR.bit.SPILBK = 1, everything comes and go as I want. If it is = 0, I get only 1's back by every command I send, it doesen't matter which one.

Saddly, I am on travel and have no access to an oscilloscope to check if the clock is working as needed, but a software check from SPISTE shows that it is doing the job.

Attached is the relevant part of my code.

As always, many thanks for your help!

Best regards,

Gustavo

#include "F28x_Project.h"

//

// Function Prototypes

//

void spi_fifo_init(void);

void InitSpi(void);

void InitSpiaGpio();

Uint16 Cmd0,Cmd1,Cmd2,Cmd3,Cmd4,CmdDummy,CmdDummy8,Cmd5;

Uint16 i,CSstate;

Uint32 rdata; // received data

void main(void)

{

// Initialize System Control:

InitSysCtrl();

// Initialize GPIO:

InitSpiaGpio();

// Clear all interrupts:

DINT;

// Initialize PIE control registers to their default state.

InitPieCtrl();

// Disable CPU __interrupts and clear all CPU __interrupt flags:

IER = 0x0000;

IFR = 0x0000;

// Initialize the PIE vector table with pointers to the shell Interrupt

// Service Routines (ISR).

InitPieVectTable();

// Initialize the Device Peripherals:

spi_fifo_init(); // Initialize the SPI FIFO

// User specific code:

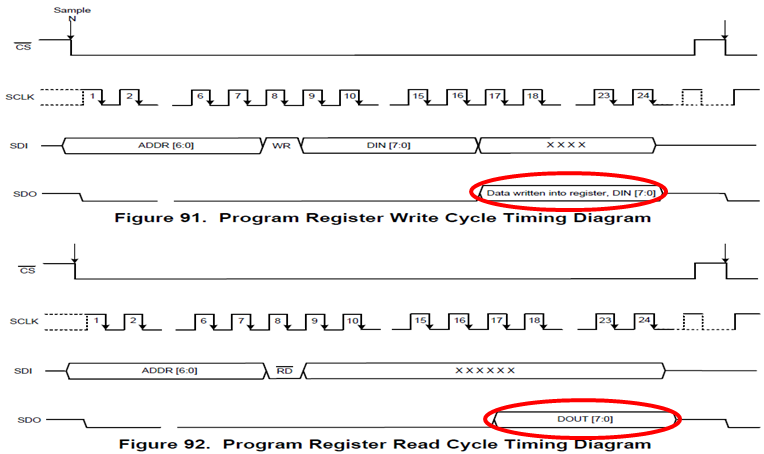

Cmd0 = 0b1000010100000000; // Reset program registers (RST) (1000 0101 00000000)

Cmd1 = 0b0000101100000110; // WRITE Channel 0 Input Range. I need 0x0110 (0000 101 1 00000110)

Cmd2 = 0b0000101000000000; // READ range channel 0 (0000 101 0 00000000)

Cmd3 = 0b1100000000000000; // Manual Channel n Select (MAN_Ch_0) (1100 0000 00000000)

Cmd4 = 0b0000000000000000; // continue with last config (0000 0000 00000000)

CmdDummy = 101010101010101001;

CmdDummy8 = 10101011;

// send data

GpioDataRegs.GPBCLEAR.bit.GPIO61 = 1; // set CS Low to start transmission

while(SpiaRegs.SPISTS.bit.BUFFULL_FLAG !=0) { }

SpiaRegs.SPITXBUF = Cmd0; // send one 16 bit command

while(SpiaRegs.SPIFFRX.bit.RXFFST !=1) { } // Wait until data is received

rdata = SpiaRegs.SPIRXBUF;

while(SpiaRegs.SPISTS.bit.BUFFULL_FLAG !=0) { }

SpiaRegs.SPITXBUF = CmdDummy; // send 18 bits dummy

while(SpiaRegs.SPIFFRX.bit.RXFFST !=1) { } // Wait until data is received

rdata = SpiaRegs.SPIRXBUF;

// Arrange data

rdata = rdata << 16;

rdata = rdata | SpiaRegs.SPIRXBUF;

rdata = rdata << 16;

rdata = rdata >> 16; // use only the last 16 bits received

GpioDataRegs.GPBSET.bit.GPIO61 = 1; // set CS high to end transmission

ESTOP0;

}

//

// END of MAIN

//

//

// spi_fifo_init - Initialize SPIA FIFO

//

void spi_fifo_init()

{

//

// Initialize SPI FIFO registers

//

SpiaRegs.SPIFFTX.all = 0xE040;

SpiaRegs.SPIFFRX.all = 0x2044;

SpiaRegs.SPIFFCT.all = 0x0;

//

// Initialize core SPI registers

//

InitSpi();

}

void InitSpi(void)

{

SpiaRegs.SPICCR.bit.SPISWRESET = 0;

SpiaRegs.SPICCR.bit.CLKPOLARITY = 0;

SpiaRegs.SPICCR.bit.SPICHAR = 15;

SpiaRegs.SPICCR.bit.SPILBK = 0;

SpiaRegs.SPICTL.bit.MASTER_SLAVE = 1;

SpiaRegs.SPICTL.bit.TALK = 1;

SpiaRegs.SPICTL.bit.CLK_PHASE = 0;

SpiaRegs.SPICTL.bit.SPIINTENA = 0;

SpiaRegs.SPIBRR.bit.SPI_BIT_RATE = SPI_BRR;

SpiaRegs.SPIPRI.bit.FREE = 1;

SpiaRegs.SPICCR.bit.SPISWRESET = 1;

}

void InitSpiaGpio()

{

EALLOW;

// Enable internal pull-up for the selected pins

GpioCtrlRegs.GPBPUD.bit.GPIO58 = 0; // Enable pull-up on GPIO58 (SPISIMOA)

GpioCtrlRegs.GPBPUD.bit.GPIO59 = 0; // Enable pull-up on GPIO59 (SPISOMIA)

GpioCtrlRegs.GPBPUD.bit.GPIO60 = 0; // Enable pull-up on GPIO60 (SPICLKA)

GpioCtrlRegs.GPAPUD.bit.GPIO19 = 0; // Enable pull-up on GPIO19 (dummy SPISTEA)

// Set qualification for selected pins to asynch only

GpioCtrlRegs.GPBQSEL2.bit.GPIO58 = 3; // Asynch input GPIO58 (SPISIMOA)

GpioCtrlRegs.GPBQSEL2.bit.GPIO59 = 3; // Asynch input GPIO59 (SPISOMIA)

GpioCtrlRegs.GPBQSEL2.bit.GPIO60 = 3; // Asynch input GPIO60 (SPICLKA)

GpioCtrlRegs.GPAQSEL2.bit.GPIO19 = 3; // Asynch input GPIO19 (dummy SPISTEA)

//Configure SPI-A pins using GPIO regs

GpioCtrlRegs.GPBMUX2.bit.GPIO58 = 1; // Configure GPIO58 as SPISIMOA

GpioCtrlRegs.GPBMUX2.bit.GPIO59 = 1; // Configure GPIO59 as SPISOMIA

GpioCtrlRegs.GPBMUX2.bit.GPIO60 = 1; // Configure GPIO60 as SPICLKA

GpioCtrlRegs.GPAMUX2.bit.GPIO19 = 1; // Configure GPIO19 as dummy SPISTEA

GpioCtrlRegs.GPBGMUX2.bit.GPIO61 = 0; // GPIO61 = GPIO61 (software controlled SPISTEA)

GpioCtrlRegs.GPBMUX2.bit.GPIO61 = 0; // GPIO61 = GPIO61 (software controlled SPISTEA)

GpioCtrlRegs.GPBPUD.bit.GPIO61 = 0; // Enable pull-up on GPIO61 (software controlled SPISTEA)

GpioCtrlRegs.GPBDIR.bit.GPIO61 = 1; // configure GPIO61 as OUTPUT (software controlled SPISTEA)

// use GPIO111 as the reset pin for the ADS8694.

GpioCtrlRegs.GPDGMUX1.bit.GPIO111 = 0; // GPIO111 = GPIO111

GpioCtrlRegs.GPDMUX1.bit.GPIO111 = 0; // GPIO111 = GPIO111

GpioCtrlRegs.GPDDIR.bit.GPIO111 = 1; // configure GPIO111 as OUTPUT

GpioCtrlRegs.GPDPUD.bit.GPIO111 = 0; // Enable pull-up on GPIO111 (RST)

GpioDataRegs.GPDSET.bit.GPIO111 = 1; // Set GPIO111 HIGH !!!! to activate ADS8694

EDIS;

}