Hello Team,

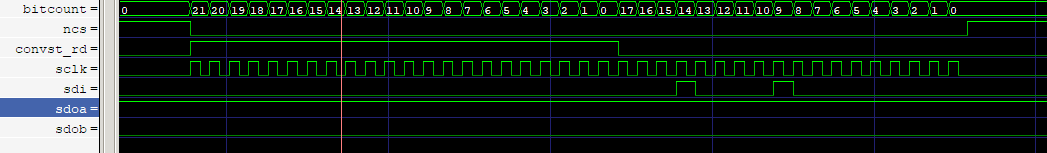

I do have a question regarding the interface ting of ADS7223. It will be connected to an FPGA. The ADC will operate in pseudo diff configuration and full-clock-mode will be enabled. Attached a simulation of the planned timing. We want to combine the CONVST and RD signals. SDO and SDA are driven with 1 or 0 on purpose in the attached example. On thing to note, which is not yet shown in the timing, are the 12ns of CONVST_RD bevor the first edge of SCLK. This will be implemented.

According to the datasheet our understanding is that when combining CONVST_RD the nCS must be set to 0 when switching CONVST_RD to 1. Is this understanding correct? We could not find a timing restriction between nCS->0 to CONVST_RD->1. In our example we have both transition at the same time. Is there a timing restriction?

Furthermore is the timing for CONVST_RD->0 for reading the data correct or does it have to happen half or a full SCLK earlier? In the example with bit count 17 we expect the MSB or the ADC channel to be reported already.

many thanks

Lutz