Other Parts Discussed in Thread: MSP430FR2633,

Hello All,

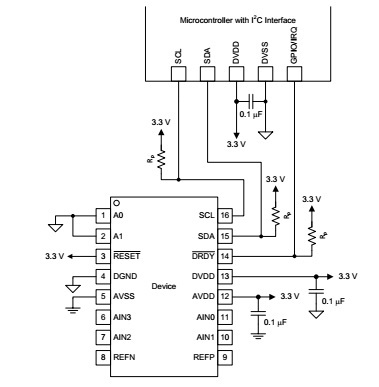

The Pin connection I did from below figure.

I'm using 10k resistor value as a pull-up and have a selected 100 kbps speed for I2C from the 8MHz SMCLK Clock.

I'm trying to interface ADS122C04 24-bit ADC with MSP430FR2633

I have written following algorithm:

1. Send Reset Command (0x06)

2. Write Configuration Register

a. Register 0 (0x40) = 0x81;

b. Register 1 (0x44) = 0x04;

c. Register 2 (0x48) = 0x00;

d. Register 3 (0x4C) = 0x00;

//Here I'm using Single short conversation mode and Single channel Read Mode

3. Send Start Command (0x08);

4.loop

{

Wait for DRDY Pin to transition low;

send Read Command (0x10);

}

The DRDY pin goes low after sending the start command.

The Above algorithm I have a implemented and I'm able to read only data = [0xFF, 0xFF, 0xFF] from ADC every time.

I'm also giving different voltage using potentio-meter on AIN0 Channel from 0 to 3.3v but I receive same data (data = [0xFF, 0xFF, 0xFF]) on different voltages.

Here is my 8MHz Clock Configuration:

{

__bis_SR_register(SCG0); // disable FLL

CSCTL3 |= SELREF__REFOCLK; // Set REFO as FLL reference source

CSCTL0 = 0; // clear DCO and MOD registers

CSCTL1 &= ~(DCORSEL_7); // Clear DCO frequency select bits first

CSCTL1 |= DCORSEL_3; // Set DCO = 8MHz

CSCTL2 = FLLD_0 + 243; // DCODIV = 8MHz

__delay_cycles(3);

__bic_SR_register(SCG0); // enable FLL

while(CSCTL7 & (FLLUNLOCK0 | FLLUNLOCK1)); // Poll until FLL is locked

CSCTL4 = SELMS__DCOCLKDIV | SELA__REFOCLK; // set default REFO(~32768Hz) as ACLK source, ACLK = 32768Hz

// default DCODIV as MCLK and SMCLK source

}

Here is my I2C Configuration:

{

UCB0CTLW0 |= UCSWRST; // Put eUSCI_B in reset state

UCB0CTLW0 |= UCMODE_3 | UCSSEL_3 | UCMST | UCSYNC; // I2C master mode, SMCLK

UCB0BRW = 0x33; // Set Bit rate 100 kHz

UCB0I2CSA = 0x40; // ADC122C04 slave Device address

UCB0CTLW0 &= ~UCSWRST; // Software Reset Disable

}

Please do needful.

Regards,

Kelvin