Other Parts Discussed in Thread: DAC5682Z, LMK04828, CDCM7005, LMK04803, LMK04133, LMK03806, CDCM6208

Hi

I am working on a university project, developing a board containing both the ADC16dv160 and DAC5682Z, both connected to an FPGA.

I need help with the clock configuration.

If it is possible I would like not to use a clock generator but drive it directly from the FPGA (LVDS signals). Alternatly a simple one.

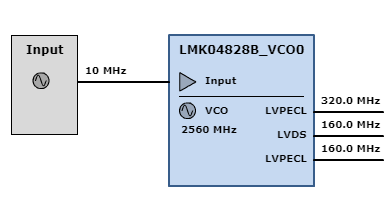

So the DAC needs a CLK signal (PECL) at 320 MHz and a DCLK signal (LVDS) at 160 Mhz. The ADC needs a CLK_IN signal (LVPECL) at 160 MHz (perhaps 320 Mhz, i am not sure).

Can I combine that somehow? not that I am very limited on connections. Due to the amound of data I only have 2 differential pairs through an FMC for the clocks.

I have combed through the data sheets but I am so confused. I hope you can help me with the design.

Should I use the same 160 MHz signal and just convert between LVDS and LVPECL or can I use the same signal for both? (the data sheet says that LVDS clock is not recommended for the ADC)

Is there a simple clock generator that only needs a 320 MHz input frequency and then output the mentioned frequencys and signal types?

Regards

Michelle