Other Parts Discussed in Thread: DAC39J84EVM

My project is using Xilinx FPGA KC705 to do DSP and transmit the processed signal together with I,Q signal by DAC.

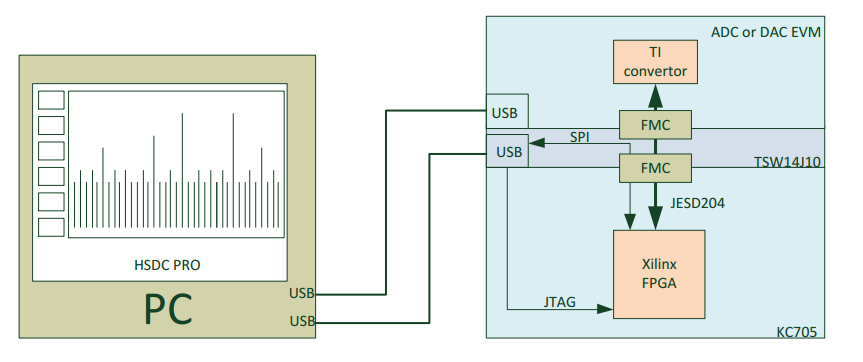

I have DAC39J84EVM and TSW14J10EVM. My set up looks like this

Q1: If I use HSDC PRO can I still use DSP or other customized algorithms in my FPGA?

If so, I only find loading the pattern and creating tones functions in HSDC, and I didn't find the part in user guide SLWU087D.

If not, is it do I still need to use the interposer TSW14j10?

Q2: I downloaded Xilinx firmware Source in the TSW14J10EVM product folder, and generated the Vivado project by running a script file. The project has the interface to the JESD204B Core and SDK source code.

Under which condition do we need to use the source code? As for me, do I need to modify the Vivado project and add my own RTL?

Q3: I need to use DAC to transmit 3 different signals from the lanes, is it possible? In the demo, after loading a pattern file, the signals from different lanes only have a phase shift. I am not sure whether it could transmit 4 completely different signals.

Could you please give me some other suggestion for my project?

Appreciate any help.

Thanks,

Star