Other Parts Discussed in Thread: ADS8681

Dear

Customer ask whether we have SPI example code for ADS8695 can be their reference? Thanks.

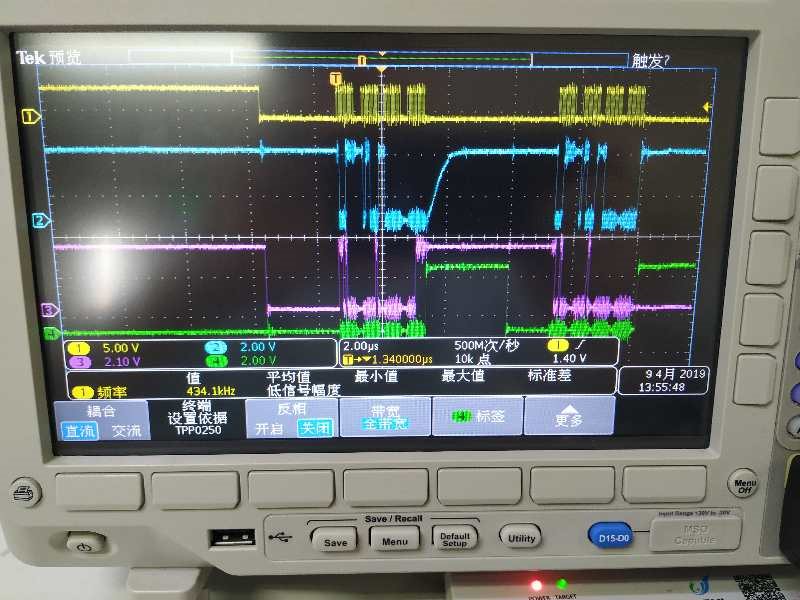

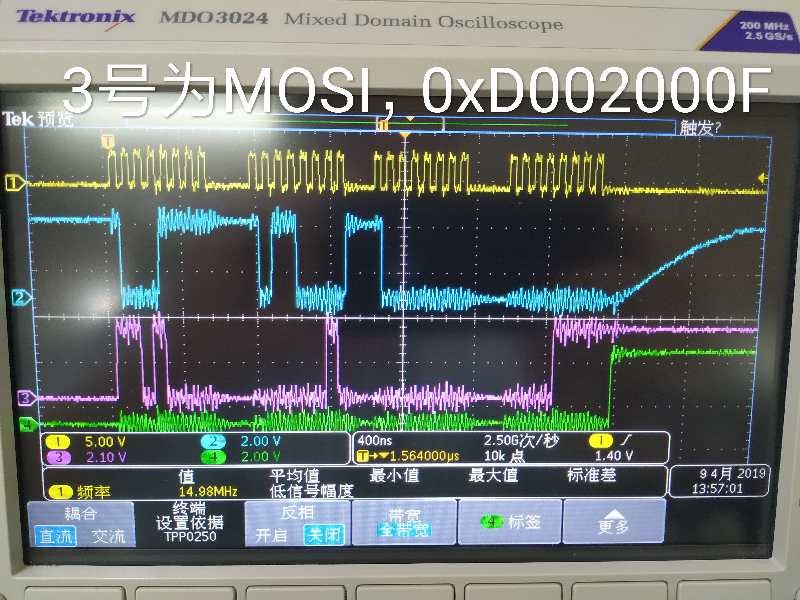

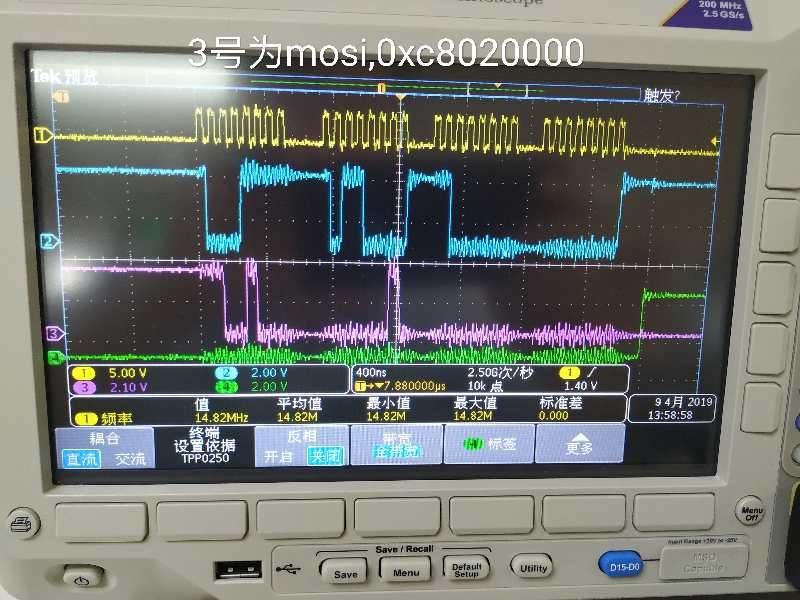

They meet a issue that whatever they set the ADS8695 register value, the read sample value always base on the default register setting.