Other Parts Discussed in Thread: AFE58JD28

Hi, there

I am using AFE5828 in our project to collect data. The AFE5828 ADC is configured to 12-bit. The PGA clamp level is set to 1.26Vpp; the LNA gain 21 dB; and the PGA gain 27 dB.

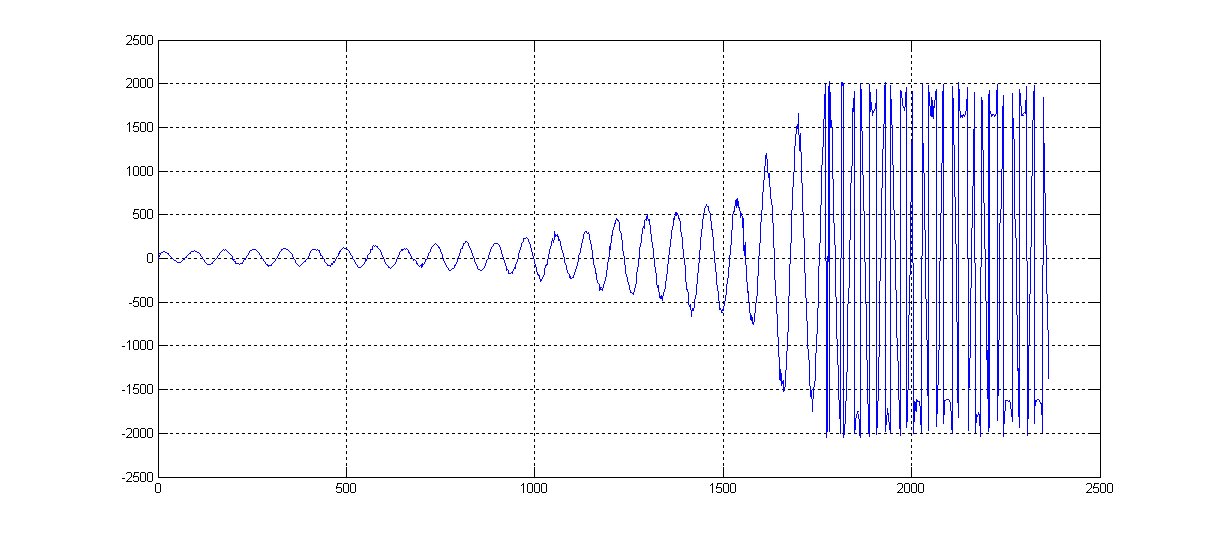

I did a test by applying a sine wave signal to the input. The collected data is plotted as follows:

The data is interpreted as signed value. The Voltage Control Attenuation is reduced with time from 36dB to 0dB.I got a doubt on this set of data: Why does the data value flip the sign when the amplitude keeps increasing? How to work around this issue? Did I miss any thing?

Looking forward to your reply.

Sincerely

FENG WU

________________________________________________________________________

Feng Wu, Ph.D.

LinkQuest Inc.

6749 Top Gun Street, Suite 100

San Diego, CA 92121

Tel: (858)623-9900, 623-9916 ext. 103

Fax: (858)623-9918

Email: fwu@link-quest.com

www.link-quest.com/sq

www.link-quest.com