Hi,

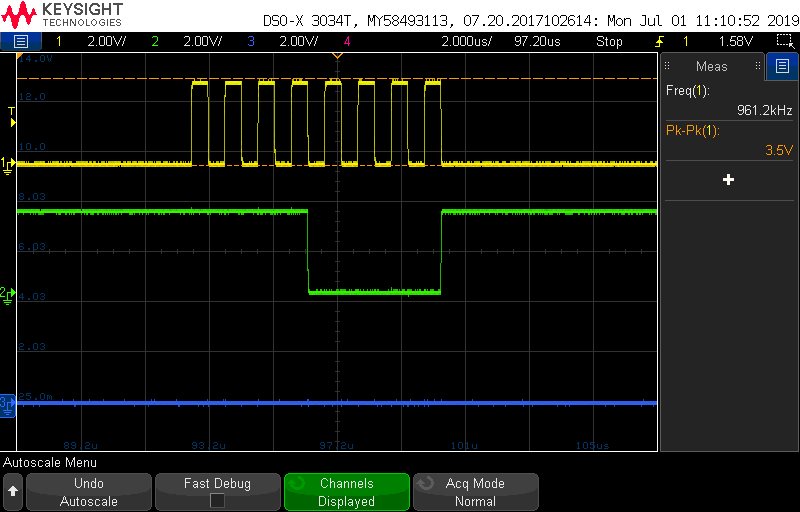

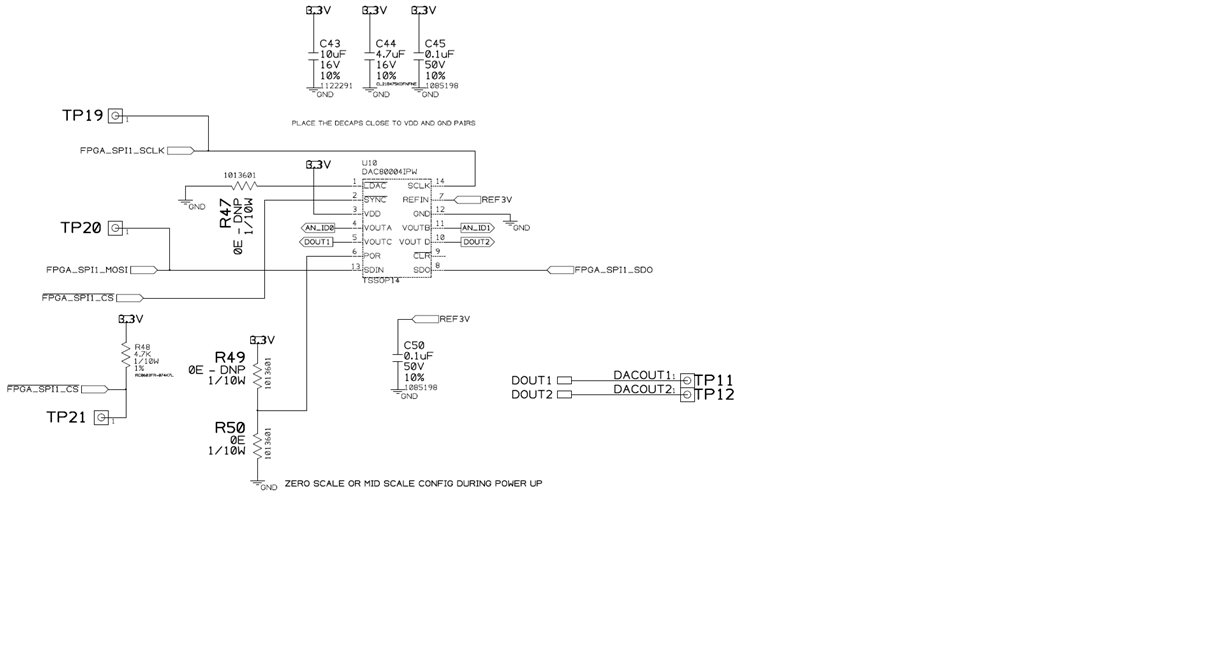

In my design with DAC80004IPW, the CLR pin is left floating. I don't see the DAC output changes with reference to the programmed DAC input code.

The LDAC pin is tied to ground through a 2K resistor and POR is connected to Ground (Zero scale). Provision for midscale is also provided(connection to VDD). The output is found working for zero scale as well as midscale hw configuration.

I would need your inputs to get this problem solved. I have attached the schematics. Please comment.

Thanks

AT