Other Parts Discussed in Thread: DAC38RF82EVM, TSW14J57EVM

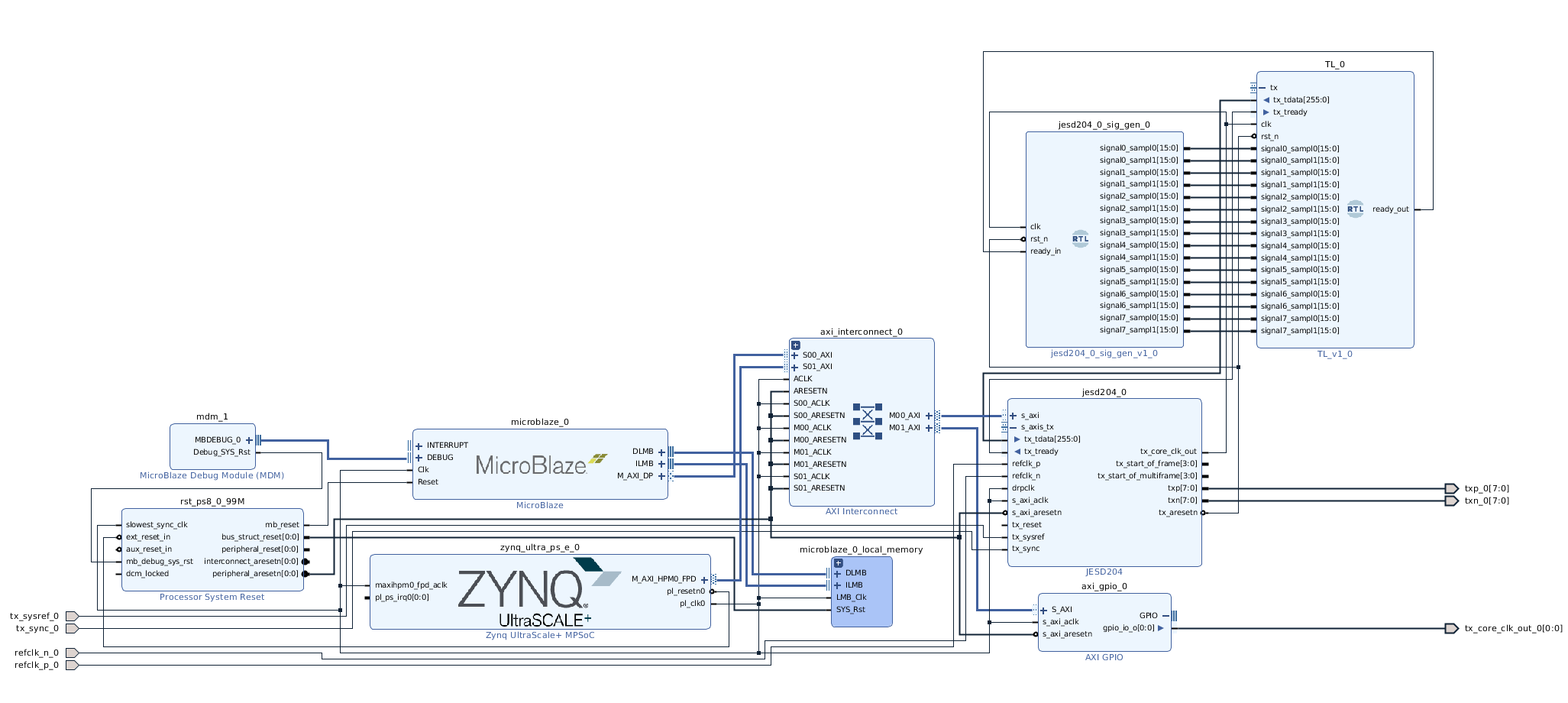

Hi All,

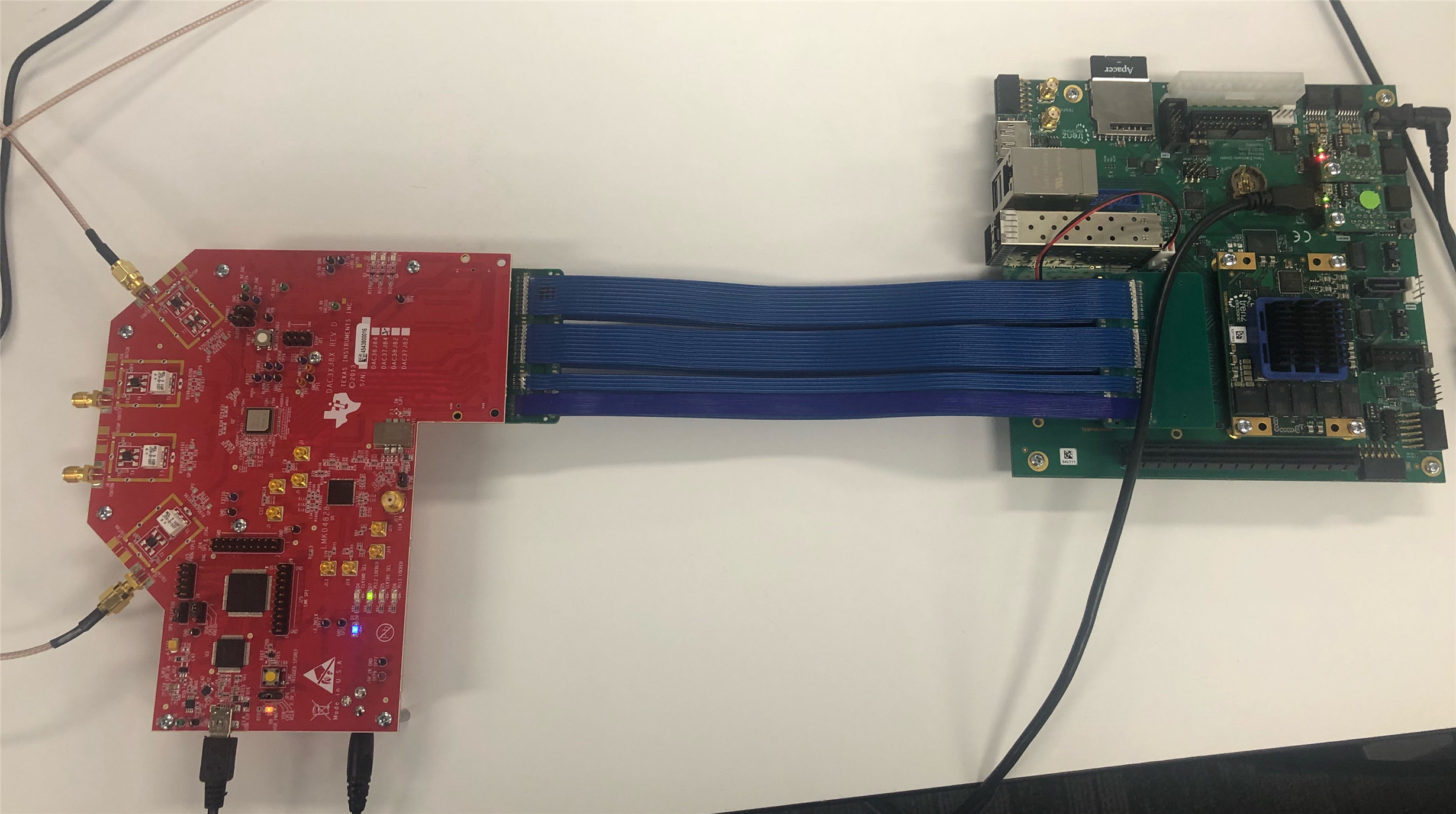

I am trying to interface DAC37J84EVM with the Zynq Ultrascale + and I need help

My approach & initial setup:

L = 8

M = 4

F = 1

K = 20

S = 1

Line rate = 7.3728Gbps

Reference clk = 184.32

1) Vivado block Diagram is shown below:

data for all signals / samples:

assign signal0_sampl0 = 'h7530;

assign signal0_sampl1 = 16'h0001;

2) I configure JESD interface in microblaze by programming registors via AXI as follows:

Xil_Out32(ADDR_start+0x004, 0x1); //RESET IPCORE

Xil_Out32(ADDR_start+0x008, 0x1); // Support ILA - ON

Xil_Out32(ADDR_start+0x00C, 0x0);// Scrambling - OFF

Xil_Out32(ADDR_start+0x010, 0x1);// Sysref - ALWAYS

Xil_Out32(ADDR_start+0x014, 0x3);// Multiframes in ILA = 4

Xil_Out32(ADDR_start+0x018, 0x0);// Test mode = Normal operation

Xil_Out32(ADDR_start+0x020, 0x0);// Octets per Frame F=1

Xil_Out32(ADDR_start+0x024, 0x13);// Frames per Multiframe K=20

Xil_Out32(ADDR_start+0x028, 0xFF);// Lanes in use = 8

Xil_Out32(ADDR_start+0x02C, 0x01);// Device subclass 1

Xil_Out32(ADDR_start+0x80C, (L << 24));// L = 7 (Number_of_lanes -1), DID = 0, BID = 0

Xil_Out32(ADDR_start+0x810, (CS << 24) |(N1 << 16) | (N << 8)| M );// CS = 0, N' = 16-1, N = 16-1, M = 4-1

Xil_Out32(ADDR_start+0x814, (HD << 16) );// CF = 0, HD = 1, S = 0, SCR = 0

Xil_Out32(ADDR_start+0x818, 0x0);// 0x818: RES1 = 0, RES2 = 0

Xil_Out32(ADDR_start+0x004, 0x1); //RESET IP CORE

NOTE: I read the regisrets back to make sure that they are correct.

3) I program the FPGA and Microblaze

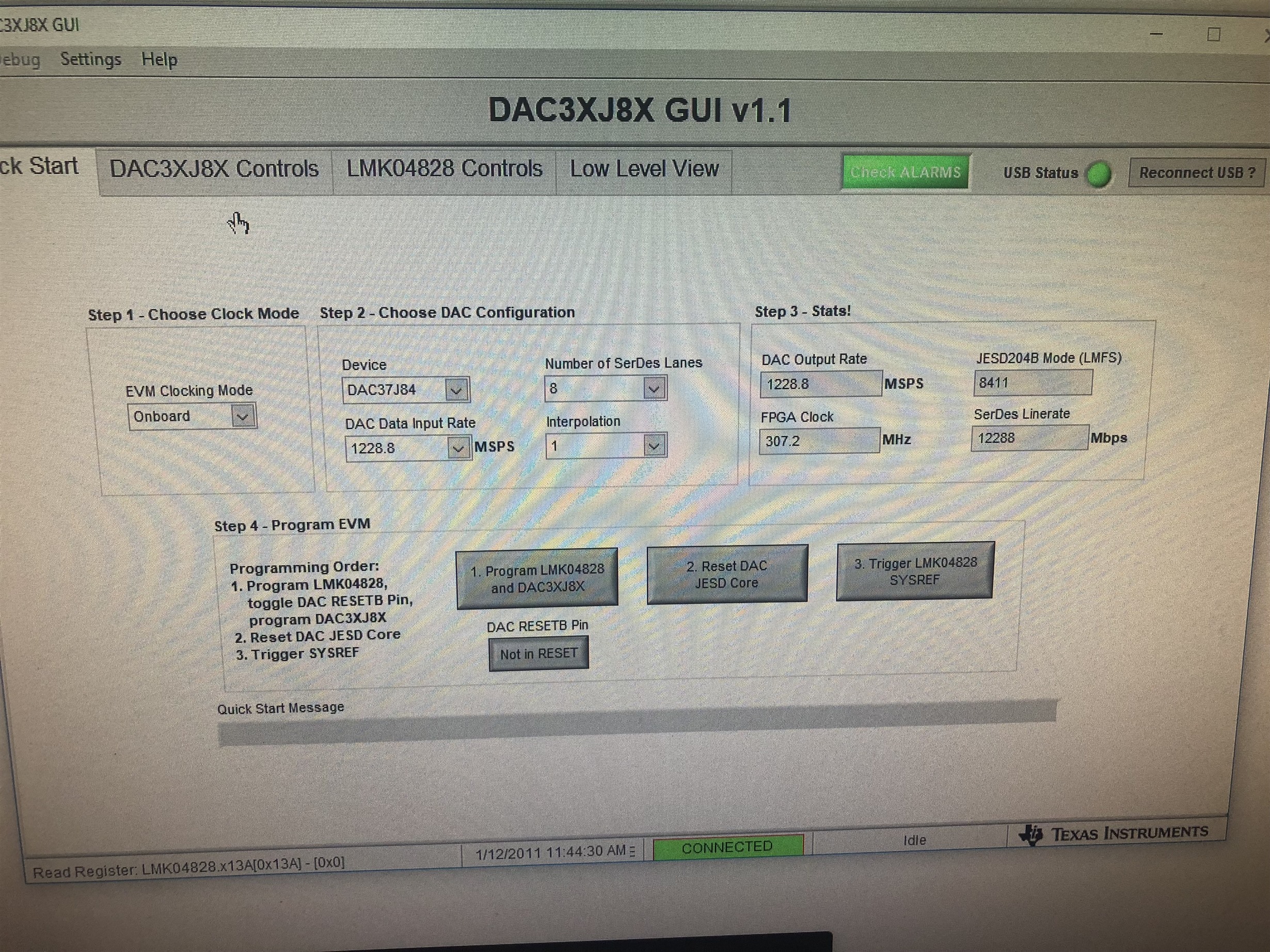

4) I program DAC via USB (DAC EVM GUI)

5) I reset JESD & trigger sysref

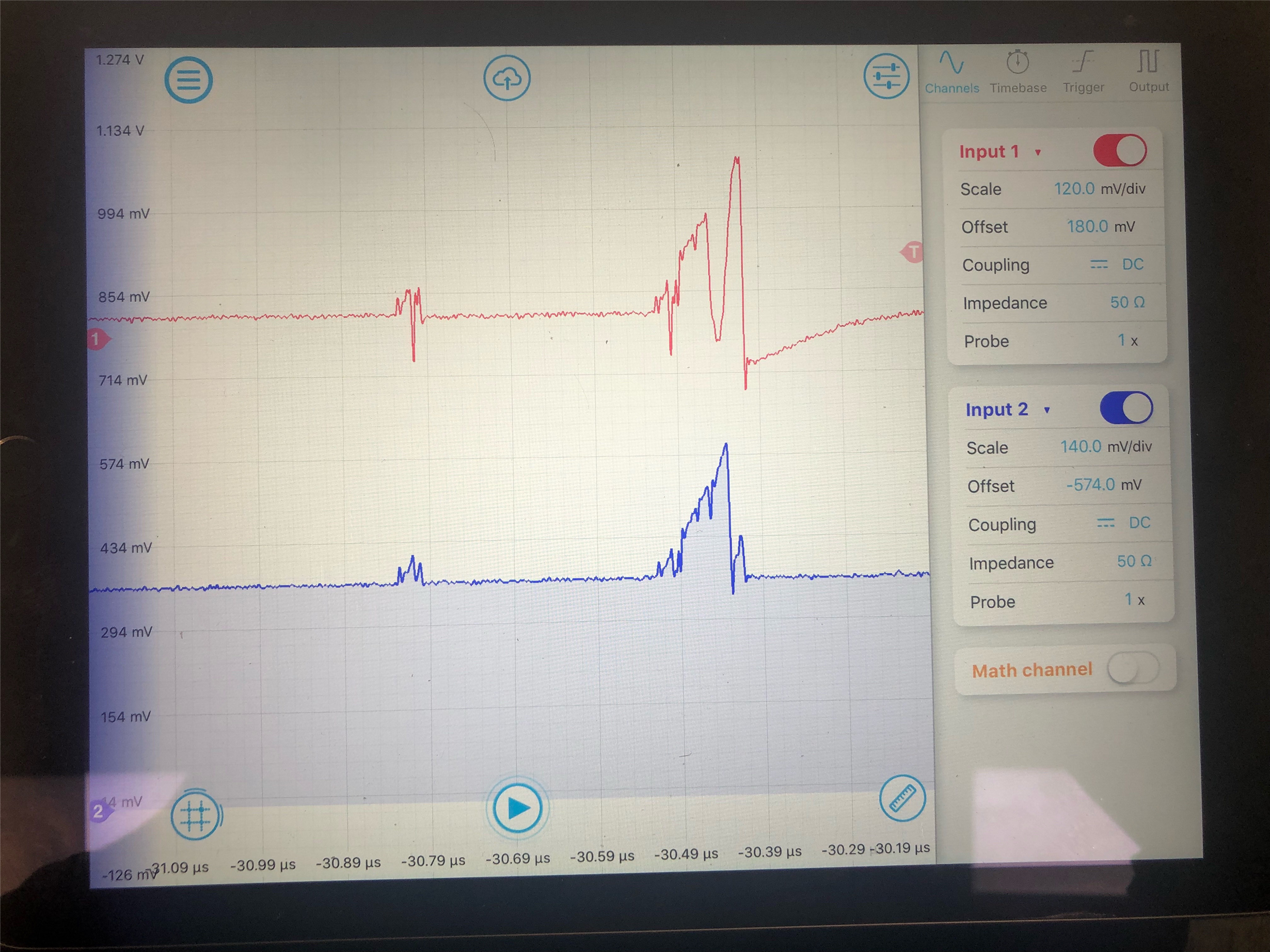

6) In the alarm window only DAC PLL is not locked. I don't see any other alarms and I cant see anything on the (oscilloscope / spectrum analyser).

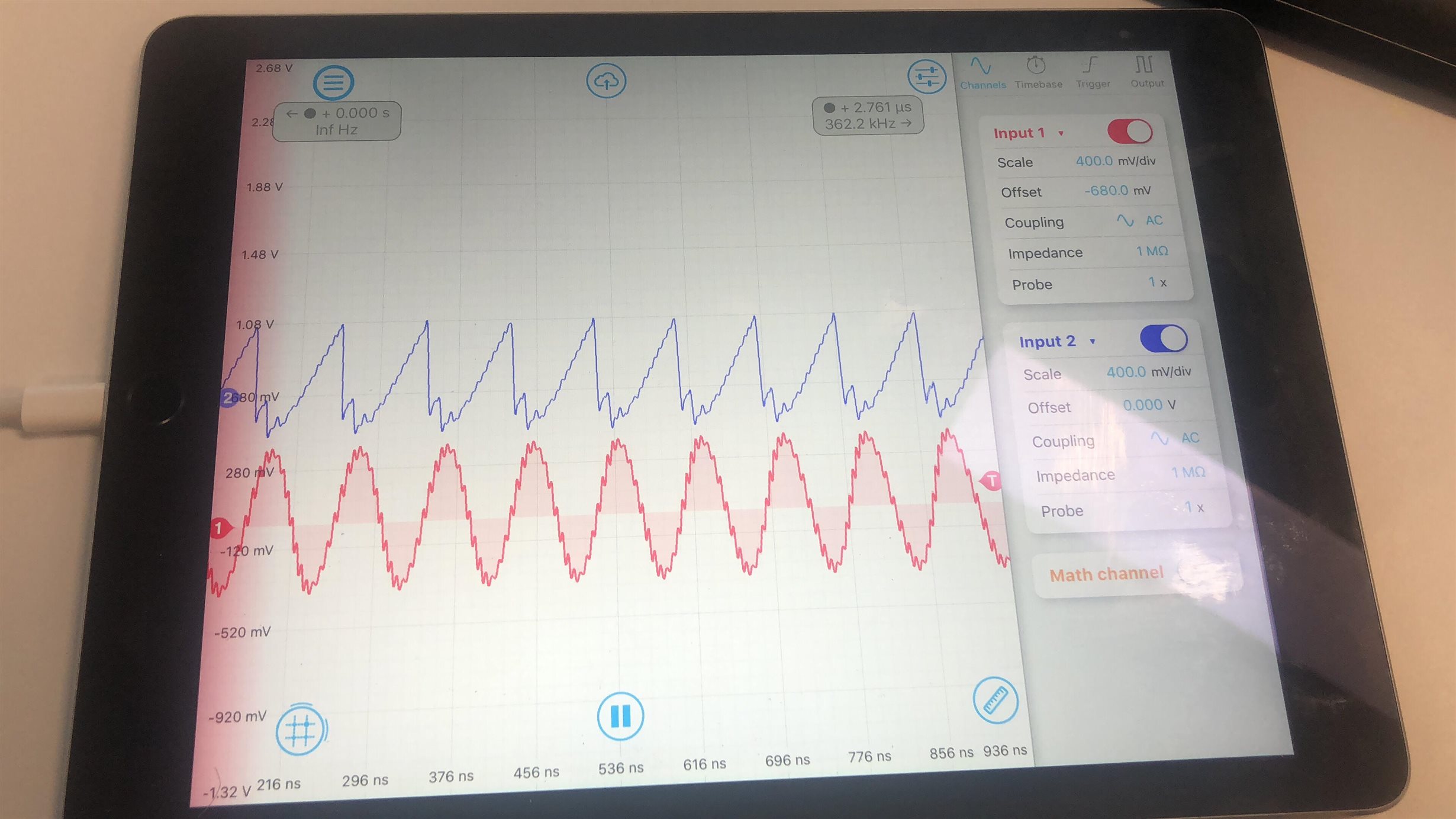

I connected clocks to LEDs. They blink as expected (after clock divider).

I am not sure how to start debugging the DAC37J84EVM JESD interface.

Any suggestions?