Other Parts Discussed in Thread: CC1101

Dear specialists,

Is there somebody who can explain the following?

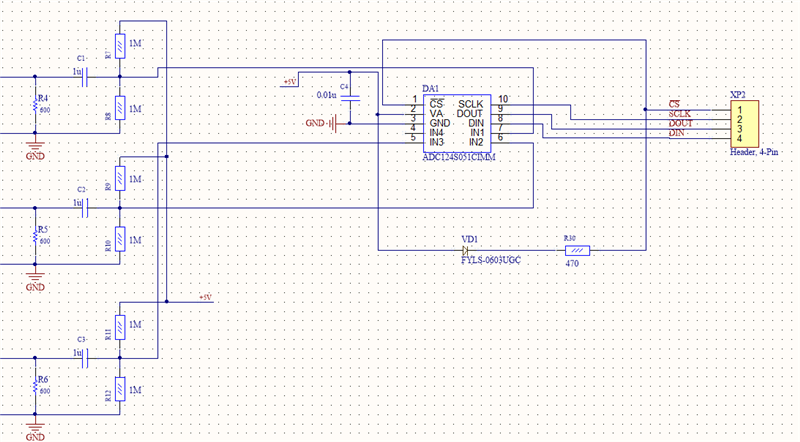

In the datasheet (page 10 for example) there is a text on the above: "FSAMPLE = 200 ksps to 500 ksps, FSCLK = 3.2 to 8 MHz, FIN = 40.2 kHz".

In the same datasheet one can find the text where it is written that the ADC starts conversion after 3d cycle of SCLK.

How can the ADC manage to covert an input signal if the ADC clock 16 times lower than SCLK (the last number can be calculated from the data)?

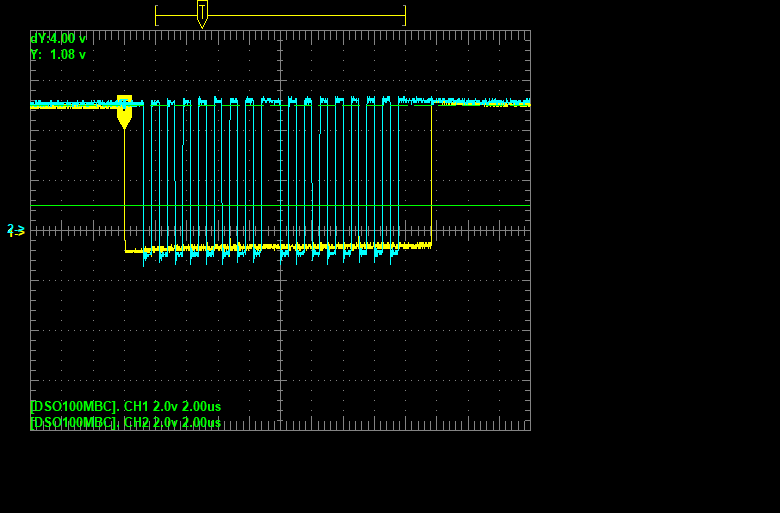

I'm trying to use ADC124S051 in some kind of voltmeter. If I measure a DC voltage I get a pretty result. If I try to measure an AC voltage the results are very inaccurate.

Thanks!