Hello,

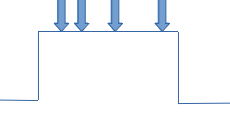

Normally driving an ADC with a higher jitter clock would be a bad idea because it reduces SNR. In our case we're over-sampling pedestals and so I don't think we'll degrade SNR. For example in the following waveform if timing is off we'd just measure the same voltage a little sooner or later:

Each of the above 4 samples still reads the same level even though timing is off. We're using a 10 nS clock and with up to say 1 nS jitter would you still expect the ADC to function well for us? I'm not sure there wouldn't be other concerns caused by increased jitter since this is a non-typical use case.

Thank you!

Regards,

Ryan B.