Other Parts Discussed in Thread: DAC3482

Hello,

We have a board where DAC3484 is connected to FPGA Virtex 6. We are feeding a 144Msps A and B channel data (IQ) to the DAC.

1. For the initial testing we have forced A channel to X"0000" and B channel to X"7000".

2. Interpolation set to x8

3. DAC is running at 1152MHz (From internal PLL). PLL reference is 384MHz

4. NCO is enabled and NCO output frequency is varied from 144MHz to 216MHz.

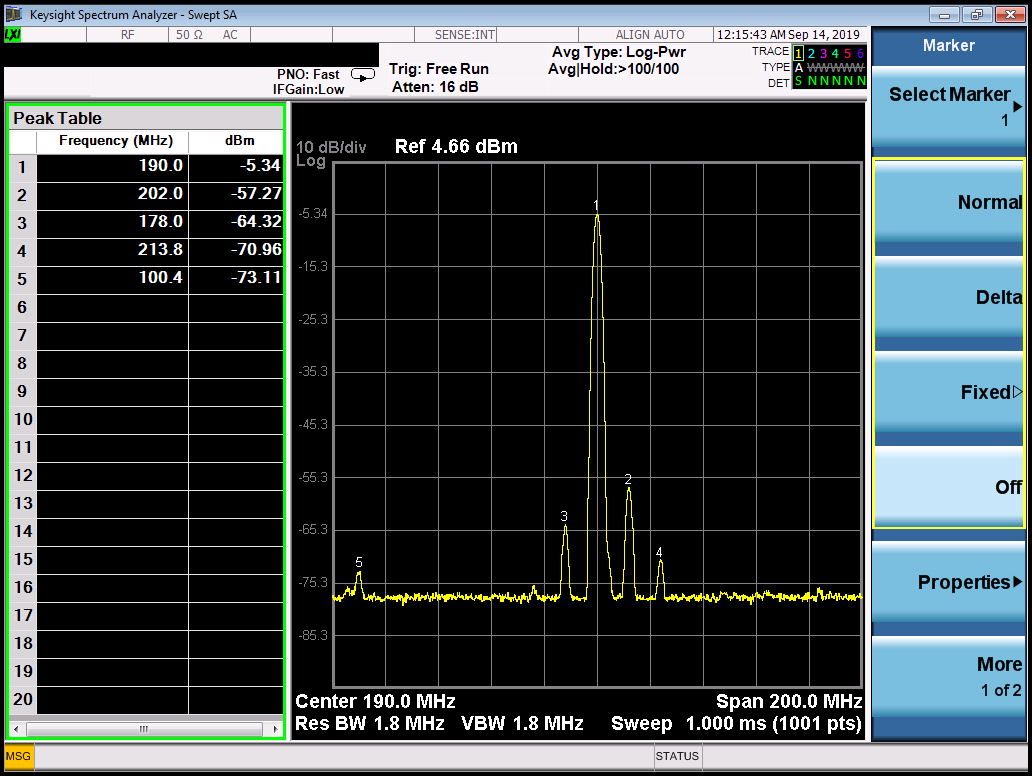

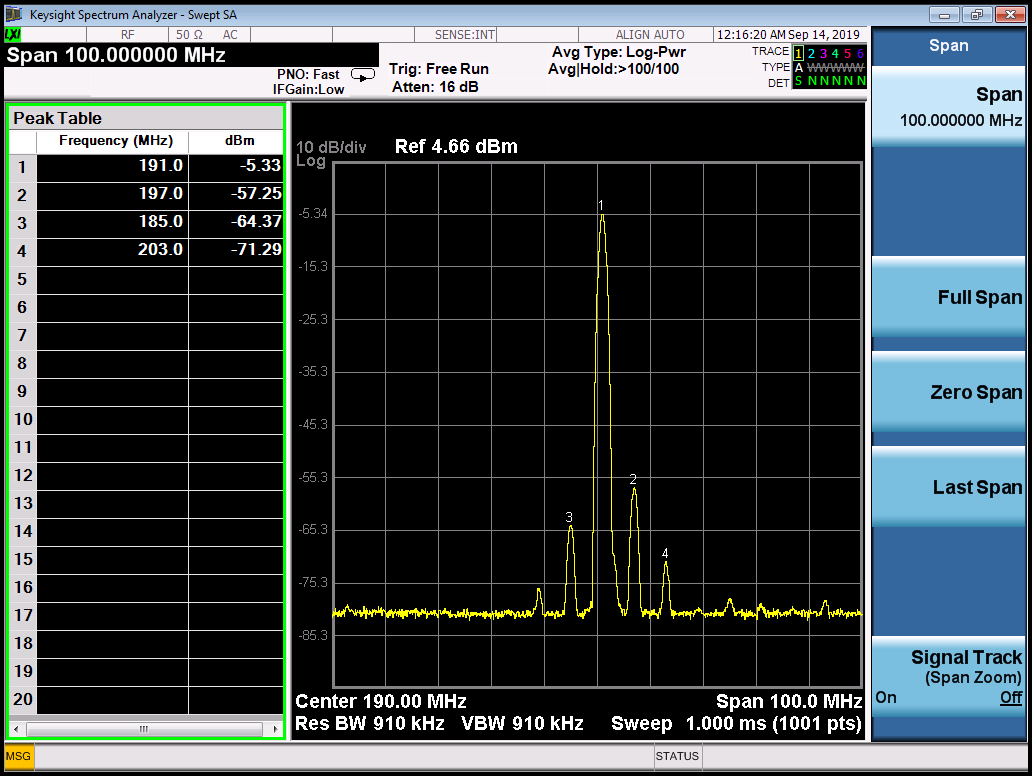

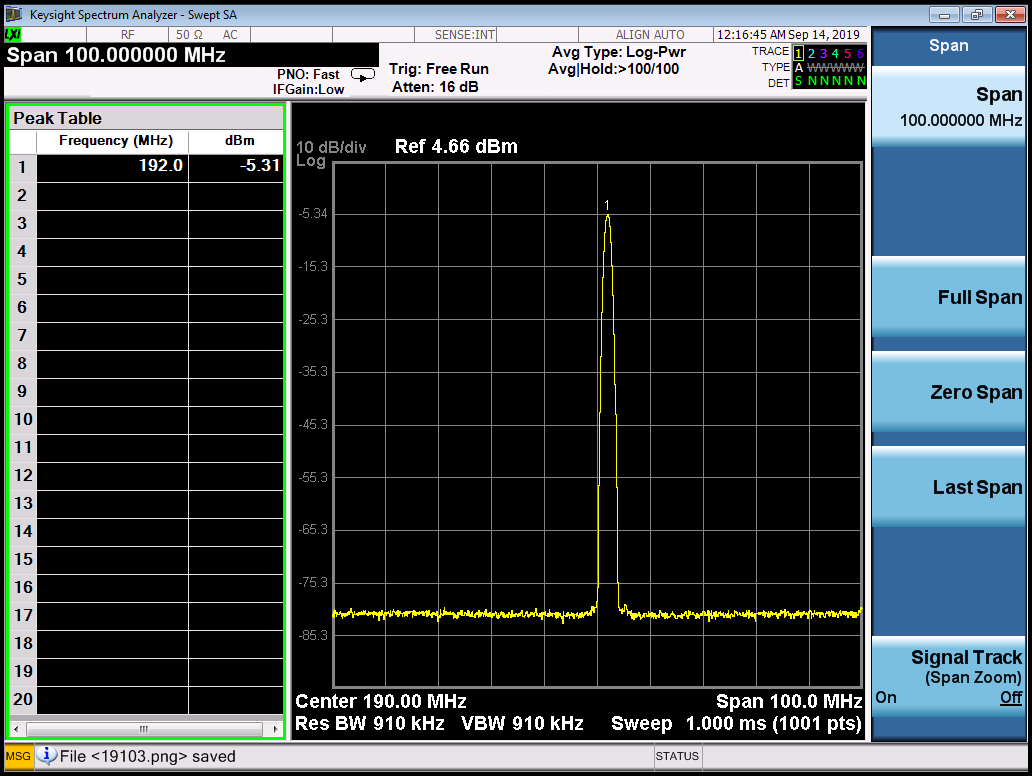

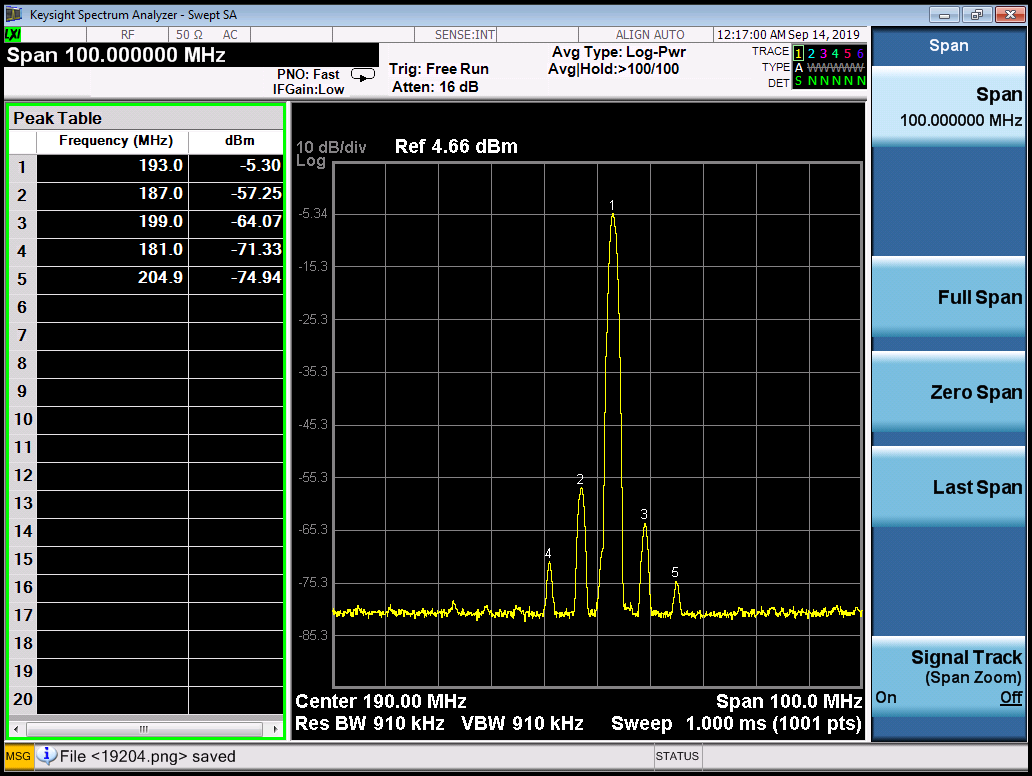

5. We have observed the following behaviour. @191MHz of output (ie. NCO tuned at 191MHz), we observed lot of extra frequency components near 191MHz Carrier peak. But when NCO is tuned to 192MHz, this behaviour disappears and SFDR improves.

6. Spectrum is attached for different NCO outputs (see zipped folder).

What could be the reason behind this behaviour?