I use the ADS8665 chip. And i want to read analog data (voltage)

The experiment environment:

1. I send the 5 voltage in Analog Ch 1 by function generator.

2. I turn on the power.

3. I send the command

(1) RST - 850000h (with 24 clk)

(2) PWR_DN - 830000h (with 24 clk)

(3) set the range in CH 1 - 0D0600h : (ch addr : 0x06 << 1 + write mode + range set : 0 ~5 V)

(4) MAN_Ch_1 - C40000h (with 24 clk)

4. repeat NO_OP - (with 32 clk)

Then the last 16 bit is read as 0xFE20. (fixed value - I change the input voltage(0v ~ 5v) or voltage range setting it is not changed)

I have some questions about act this chip.

1. There are any setting to read analog data?

2. The data bit analysis - The analog bits is 12 bit -> 0xFFF - 1 is the max value ( ex) if range set(0 ~ 5V) and input voltage is 5V. Then, The SDO bit is 0xFFE.) It is right?

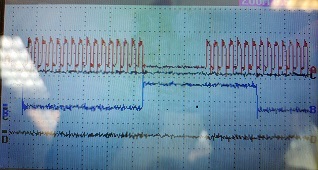

3. I have some hold time - cs_low. Because the master chip can send max bit 16. So, If i send the 32 bit, I send 16 bit and have some delay(In the figure, the red line low area between clk act) and send the extra 16 bit. It is no problem to read data?

(spi wave - there is no cs(but I confirm the cs act alright). red(a) - clk, blue(b) - miso, green(d) - mosi, block(c) - input voltage(5v))