Other Parts Discussed in Thread: LMK04828, , LMX2582, LMX2592

Hi,

We are using three DAC38RF80 in our design. For clocking we are using LMK04828 ,LMX2582/92 and HMC987.

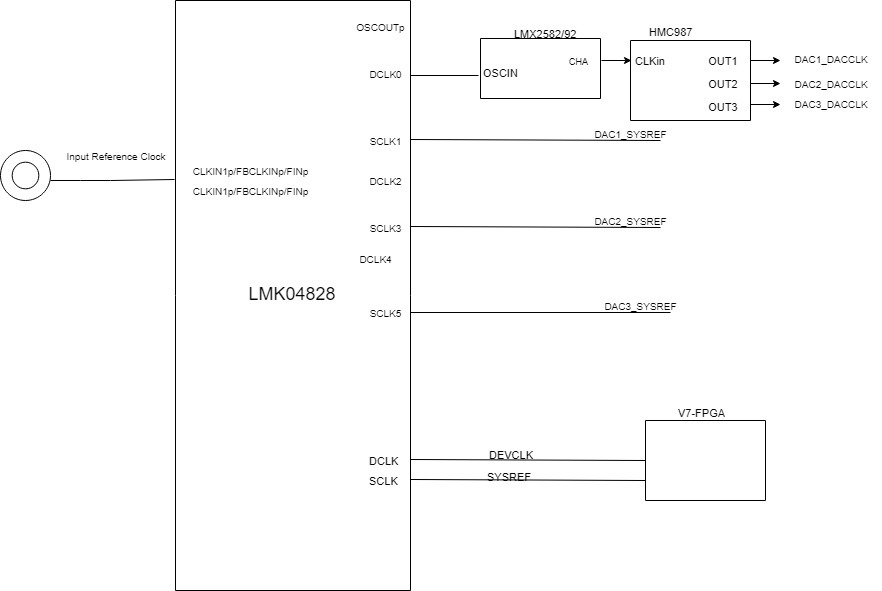

Clock tree is shown below:

One output of LMK04828 is connected to refclk input of LMX2582/92. Channel A of LMX is connected to buffer HMC987 which buffers the input and then three output of HMC987 is connected to DACCLK inputs of three DACs.

SYSREF clock for synchronization is provided by LMK04828.

Although DAC has internal PLL and we can directly fed the DACCLK inputs of three DACs from LMK04828 as shown below, but it is written in the datasheet of DAC38RF80 that for best performance of DAC38RF80 use DAC in PLL bypass mode:

So my question is:

1. Which configuration from the above two block diagram will give the best performance both in case of noise and synchronization? We will be using the DAC at maximum sampling frequency 9GSPS.

2. Will there be any difference in DAC performance when we use internal PLL of DAC using LMK04828 output as reference for DAC PLL vs using DAC in PLL bypass mode and use LMX2592 output as sampling clock for DACs. LMX2592 itself receives its reference from LMK04828.

An early response will be highly appreciated.

Thanks,

Lalit