Other Parts Discussed in Thread: DAC38RF89

hello,

We have a one JESD204B master implemented on a Xilinx FPGA (ULTRASCALE device).

In the FPGA configuration M=2, L=8 (LMFS).

Eight serdes lanes are connected to the DAC38RF82.

We have a 16bit/2.5Gbps mode in which four lanes are connected to DAC A in the DAC38RF82 and four lanes are connected to DAC B (ONE_DAC_ONLY=0, ONE_LINK_ONLY=1).

The physical connections are as follows:

FPGA DAC38RF82

TX0 RX1

TX1 RX4

TX2 RX6

TX3 RX7

TX4 RX5

TX5 RX0

TX6 RX2

TX7 RX3

Polarity should be inverted (in the DAC) for TX0, TX2, TX5, TX7.

The JESD mode we use for the 16bit/2.5Gsps is LMFSHd=82121.

In the FPGA, TX0 uses lane ID=0, TX1 uses lane ID=1 and so on for the rest of the TXn.

FPGA TX0-TX3 are routed to DAC A of the device (via the cross-bar, lane enable, etc.).

FPGA TX4-TX7 are routed to DAC B of the device.

My questions:

- Using Table 9, JESD204B Formats for DAC38RF82 and DAC38RF89 (p. 30 in the datasheet):

We use the mode in last table entry (41121 / 82121).

It seems the mode we require is 2 TX, 82121.

What is the difference between 1 TX and 2 TX? (we use ONE_DAC_ONLY=0, ONE_LINK_ONLY=1). - Using Table 41, Register Programming for JESD and Interpolation Mode (p. 52 in the datasheet):

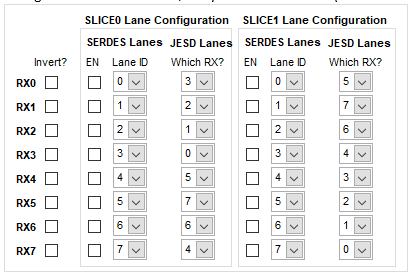

Which mode is the correct one for us: 82121/NA or 41121/82121 ? - Giving the above information, can you fill the enclosed (from DAC38RFxx EVM GUI):

(or supply with the relevant registers settings)

Thank you !

Gil Hershman