Other Parts Discussed in Thread: DAC37J84, DAC38J84

Hi,

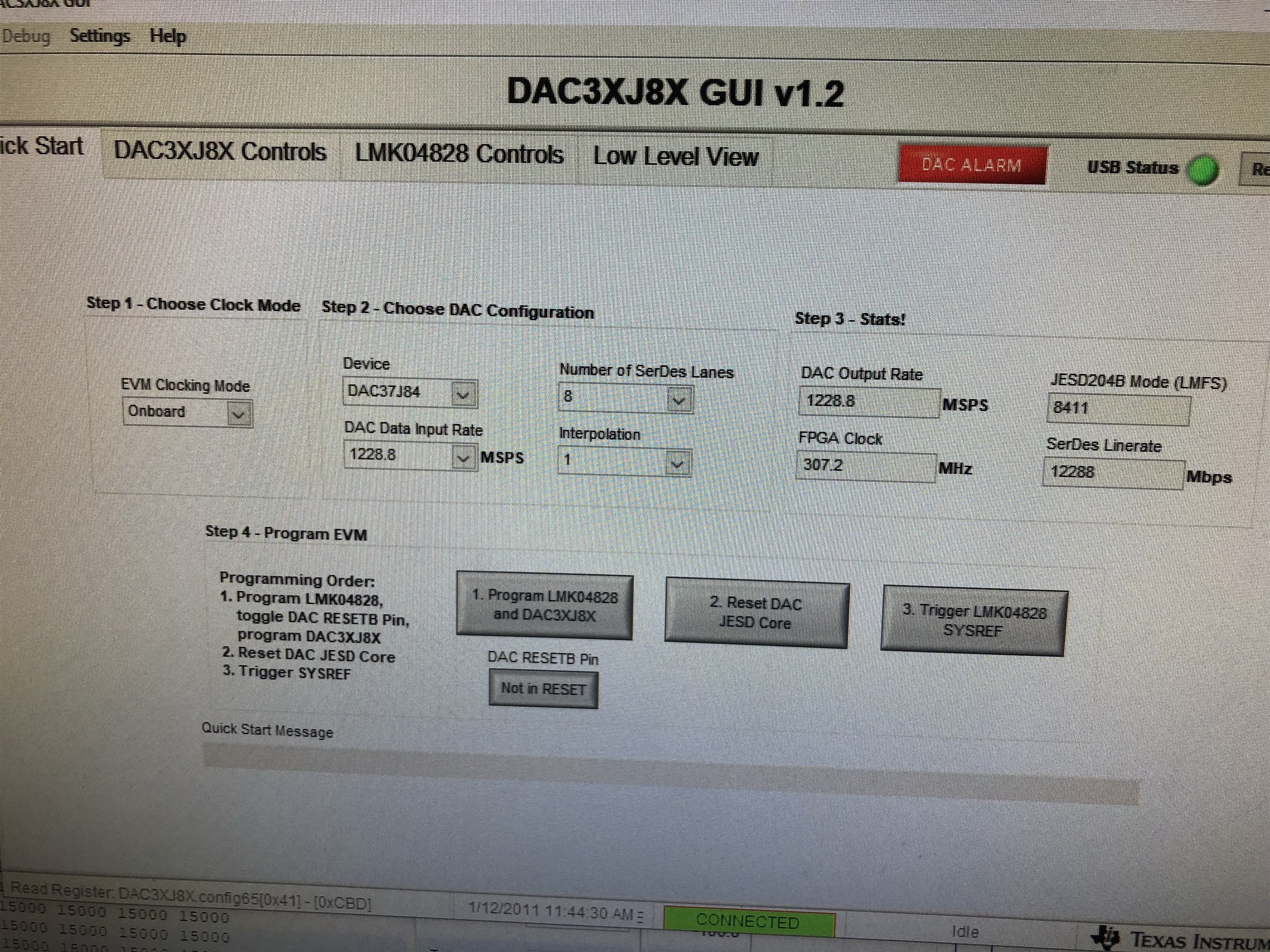

I am running 12.288 GB JESD link (scrambling off) between TSW14J56 and DAC37J84EVM.

I can see the data, however, DAC GUI shows a large amount of 8b/10b errors happening and NO alignment errors. A large amount of errors causes the link to resync and the output waveform will disappear during resync.

Also, I noticed that with scrambling I am getting less 8b/10b errors (0-5000 and slowly increasing) but more alignment errors (Overall link 0 error count is less than without scrambling).

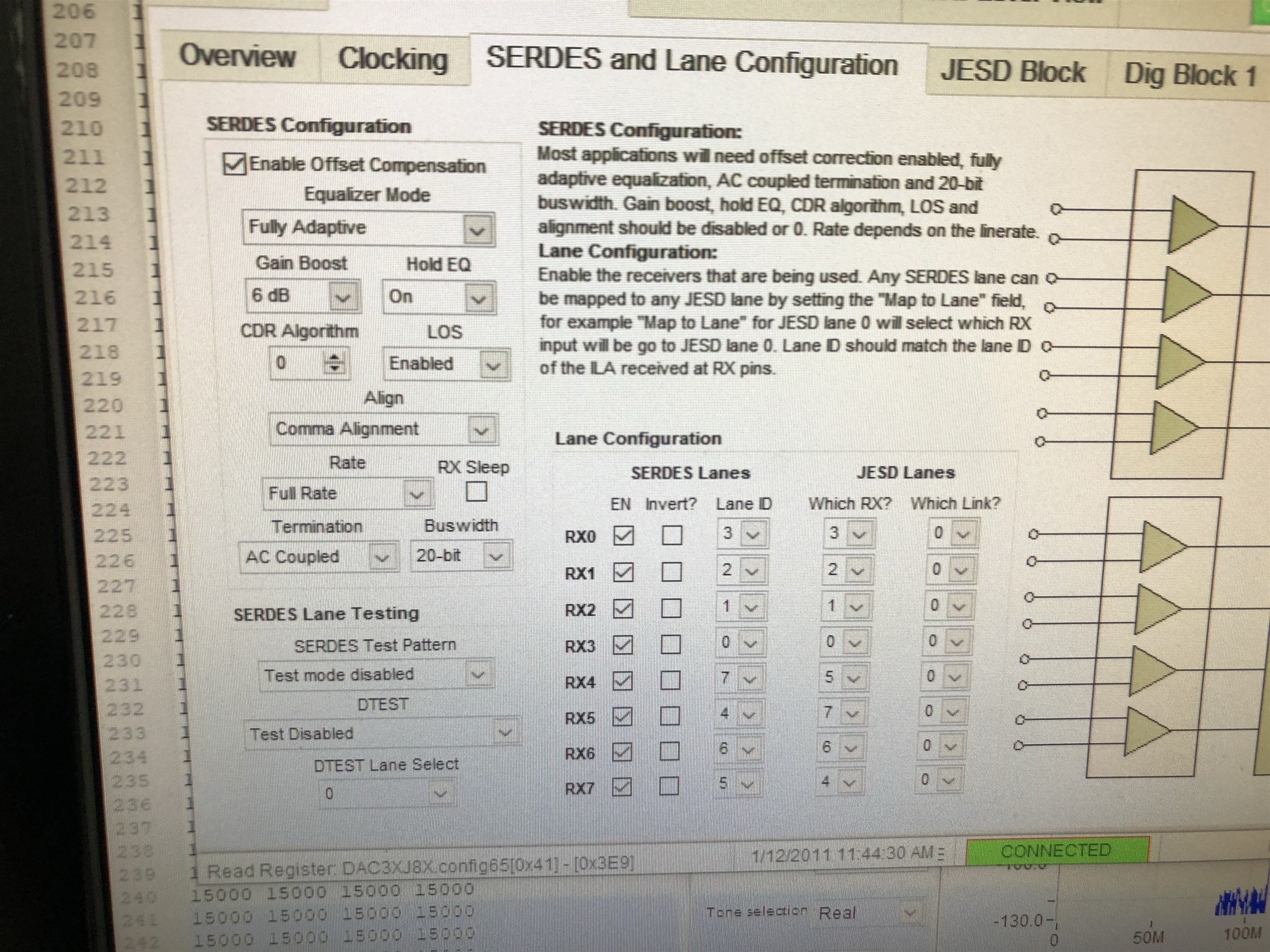

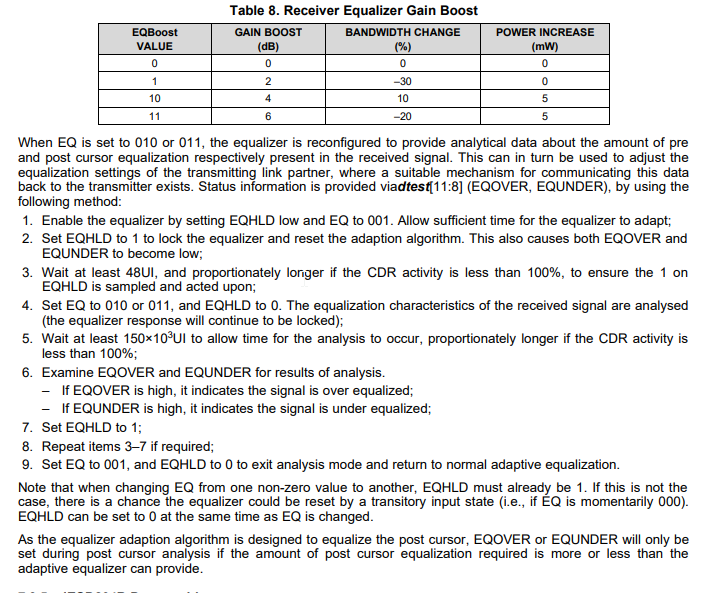

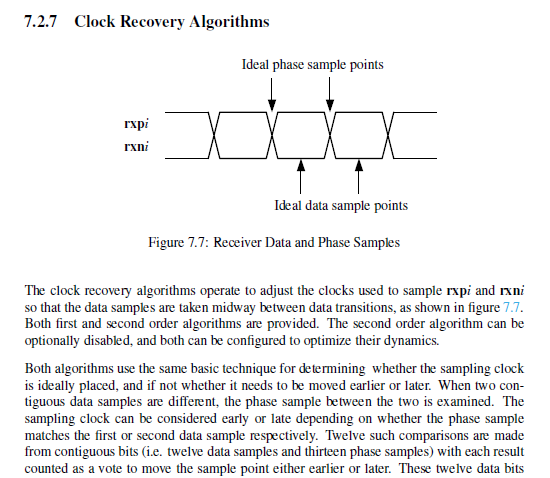

1) On the custom build board what could be done to improve the BER?

2) From the data sheet it is not clear how to use the eye-scan. Do I need JTAG for that? Can this be done with SPI?

3) Do I need additional software to run eye-scan?

Cheers,

Anton