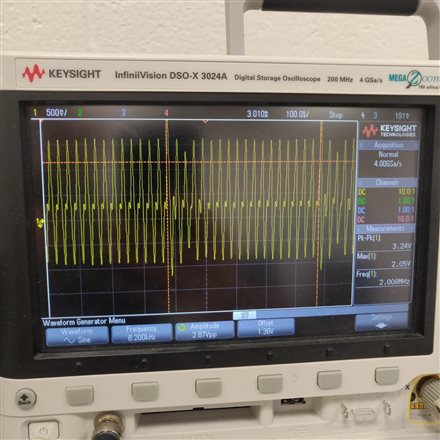

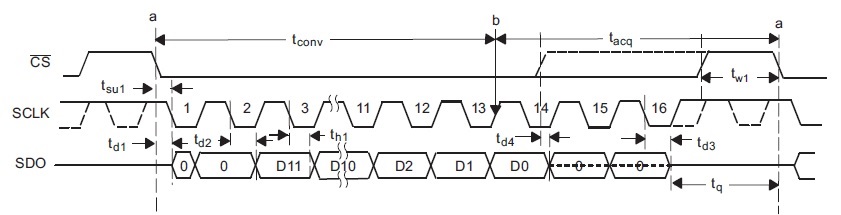

The datasheet defines the characteristics of the ADS8873 at 32MHz and 48MHz clock frequencies. Are these the maximum clock values or the can the device work at lower frequencies, and lower sampling rates) as well? I tried with lower frequencies, e.g. 8MHz, but my results are inconsistent

Thank you