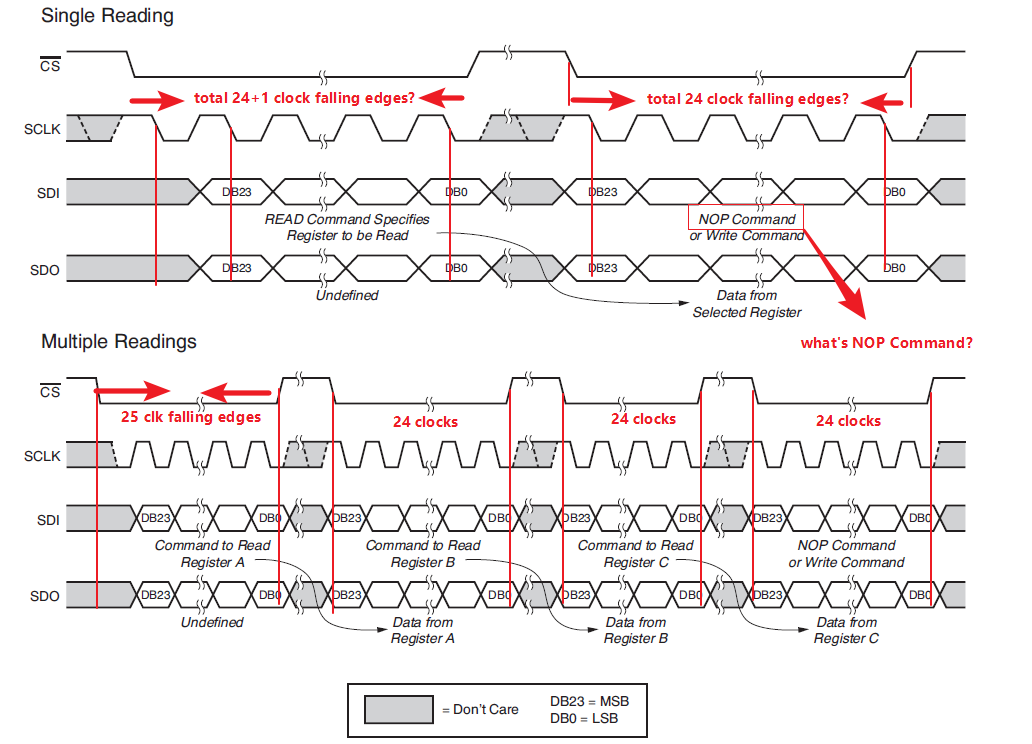

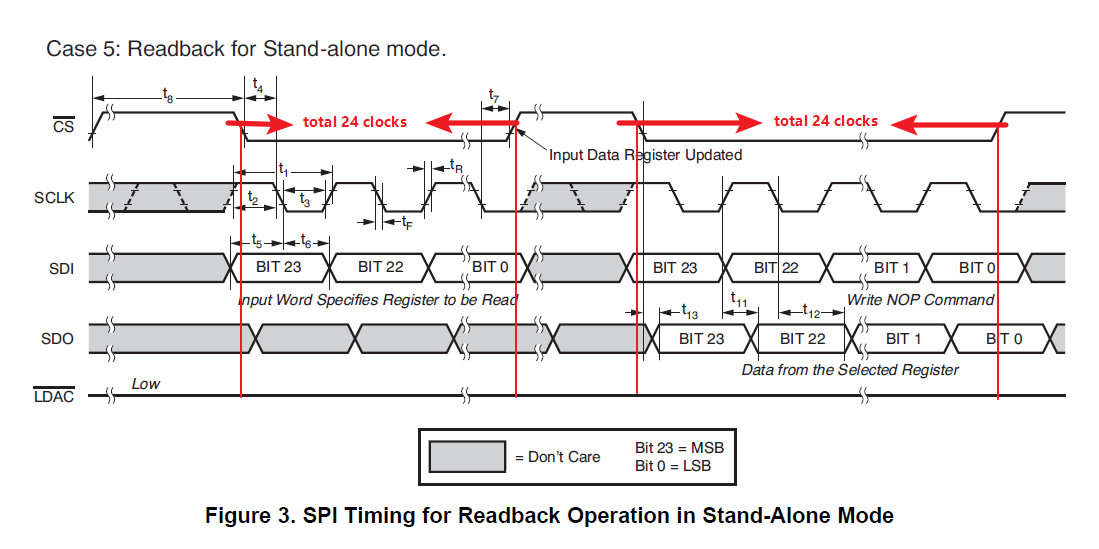

once I dereset the DAC8734, the value of the reg0 should be 0x003C, but the chip returns 0x0000, I'm sure the chip is dereset and Load pin is tied to GND.

I have 45 DAC8734 chips on my PCB borad, and only a part of them are read failed.

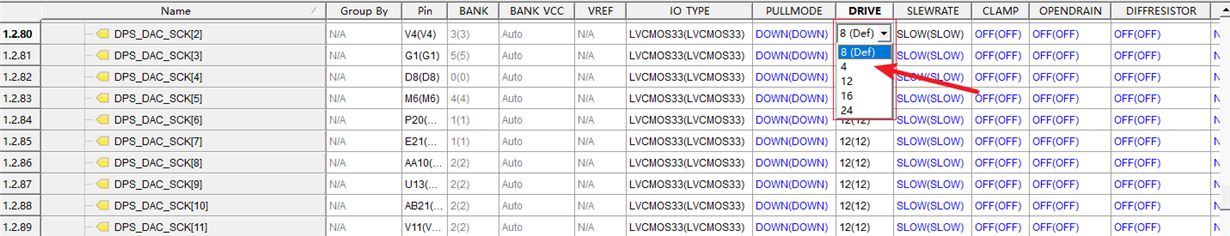

I change the master SPI code version of my FPGA (all 45 chips are accessed by the SPI from a FPGA), and some chips can't be read before become OK, but some OK before, fail after.

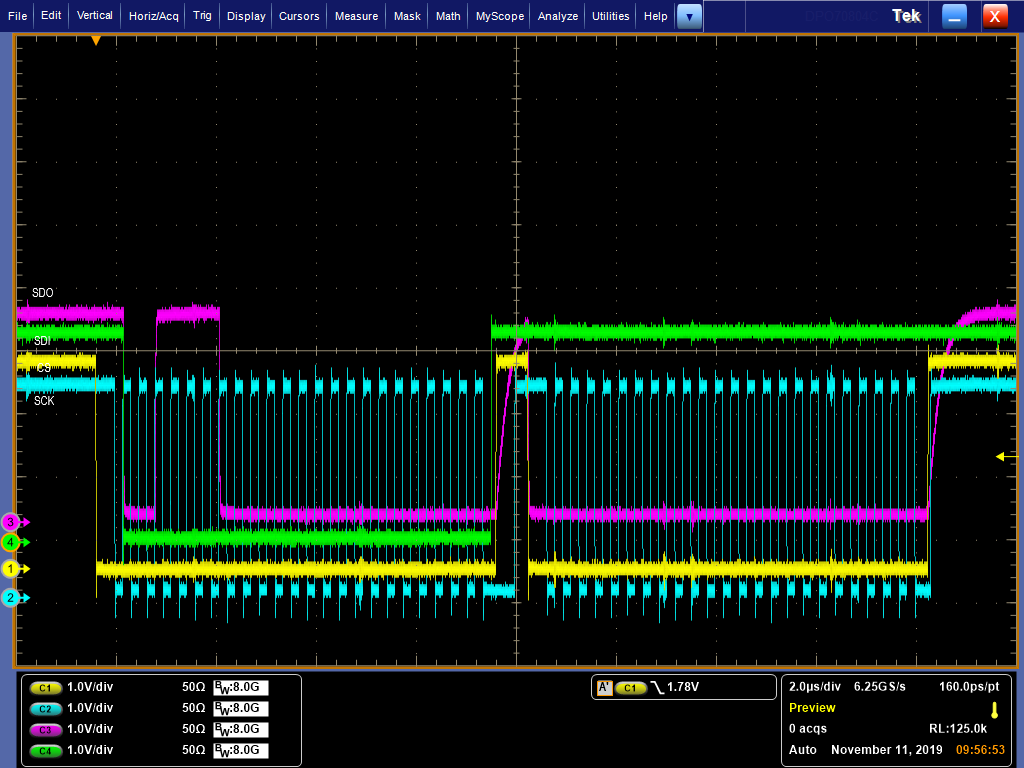

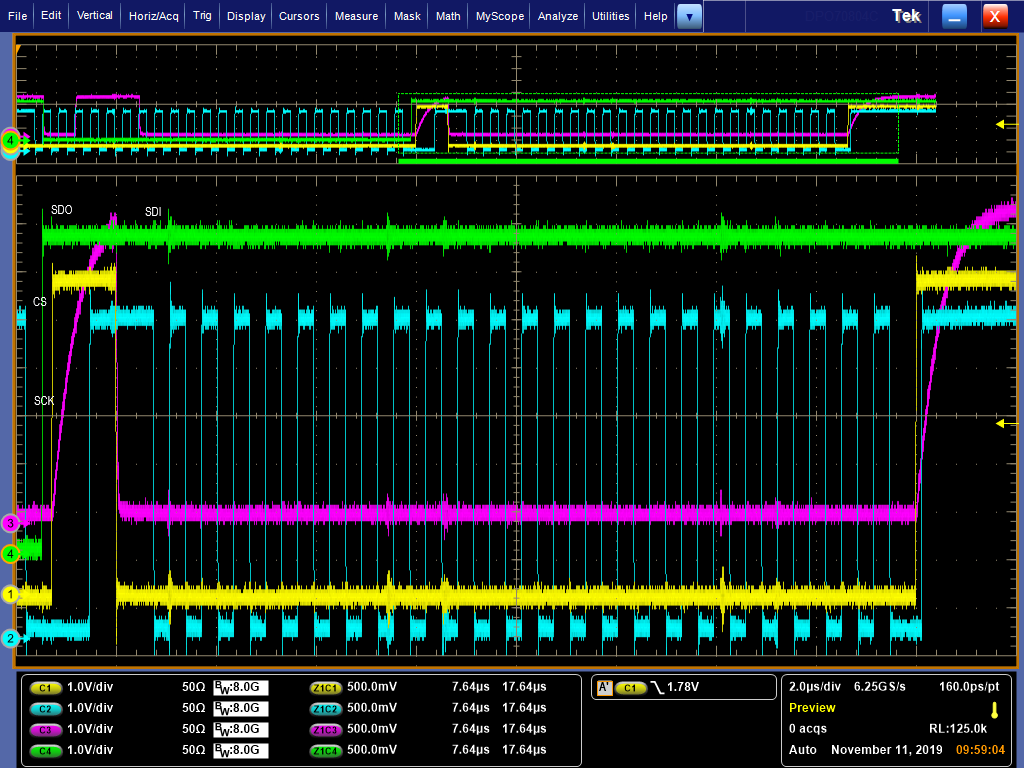

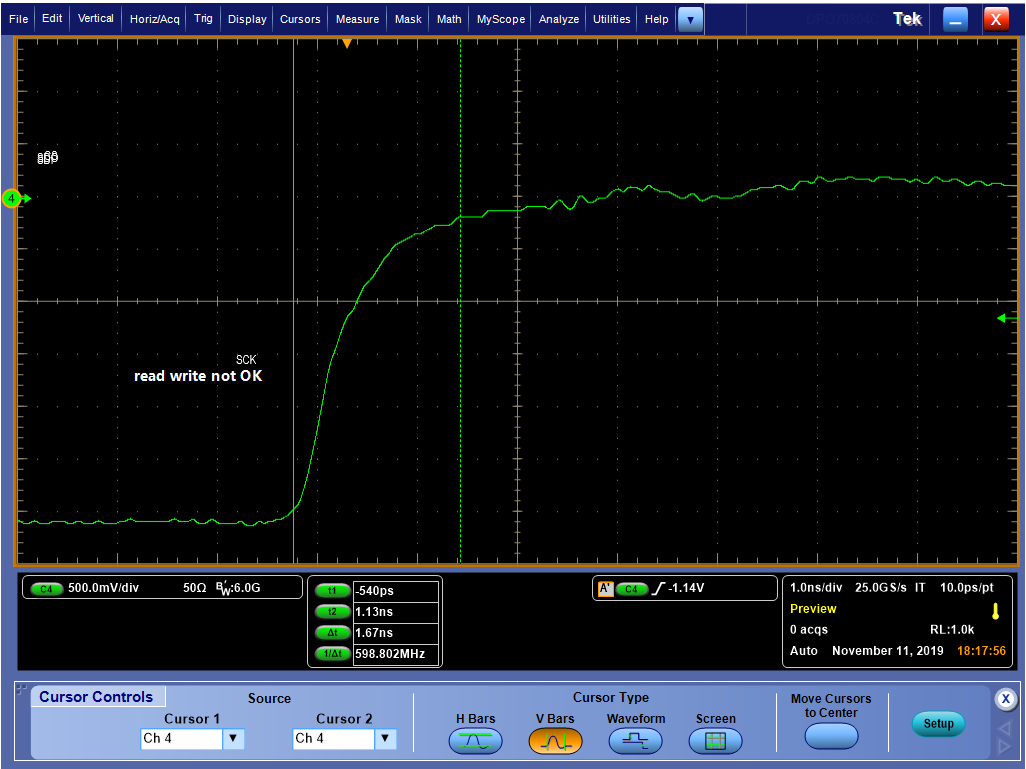

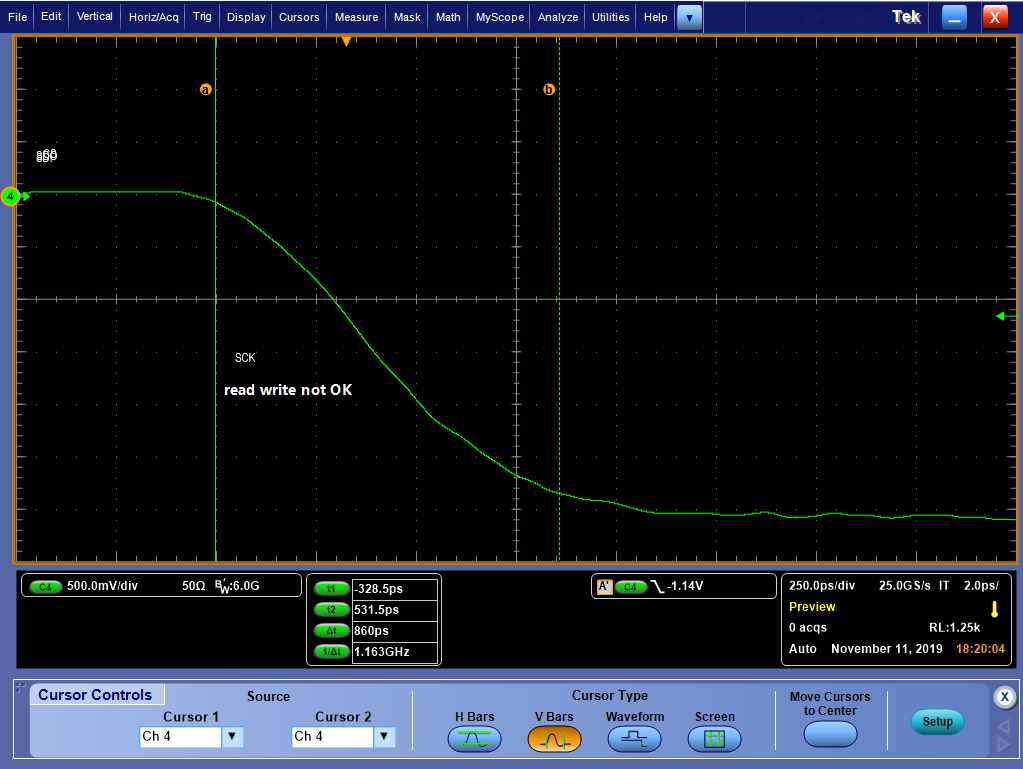

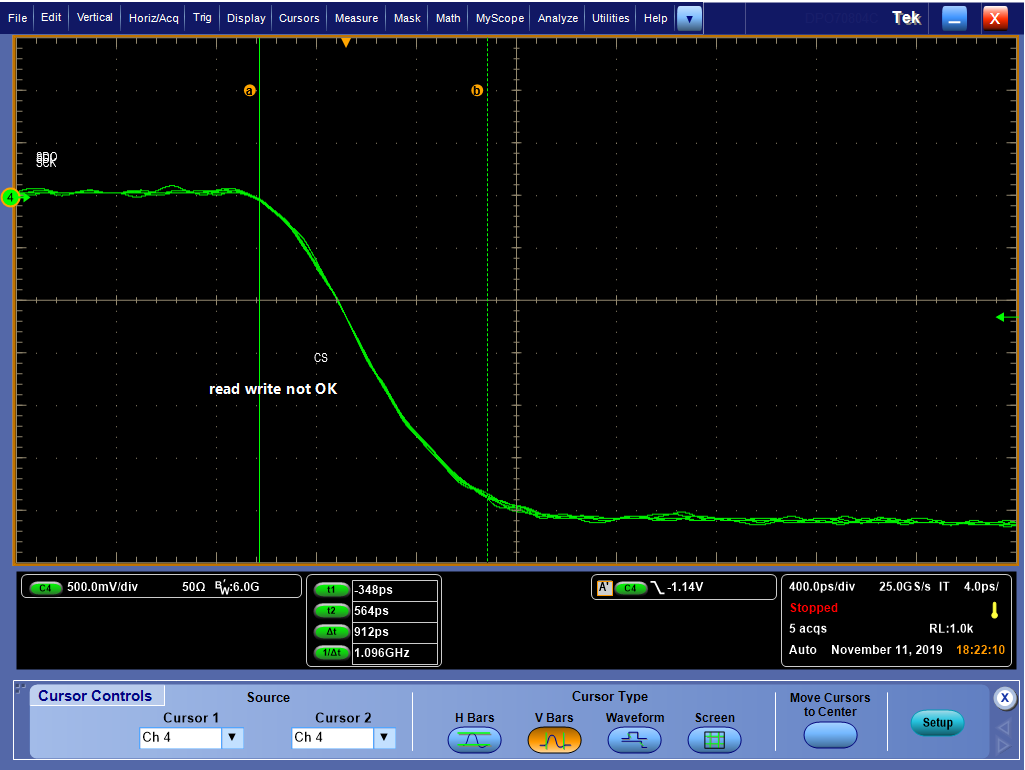

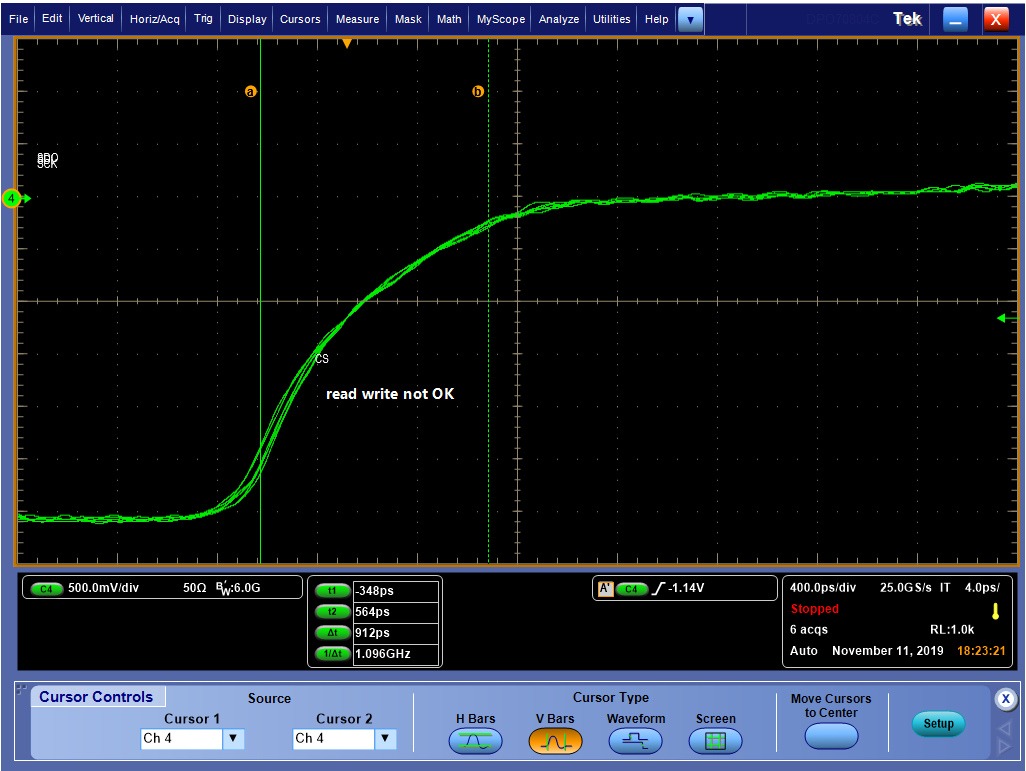

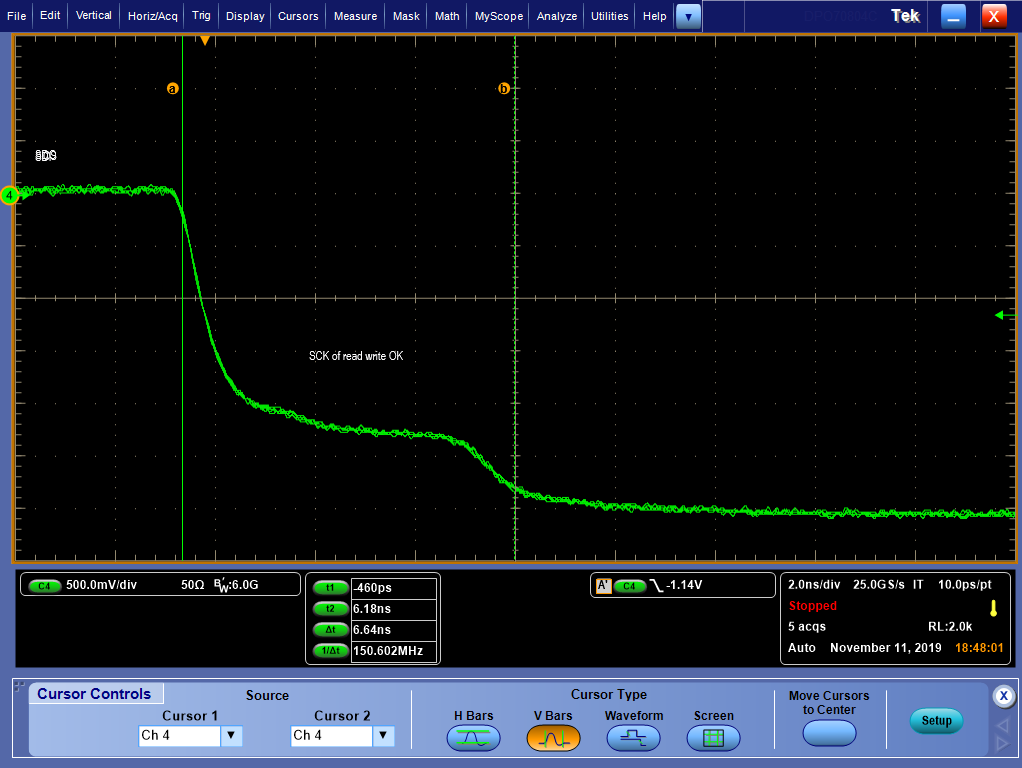

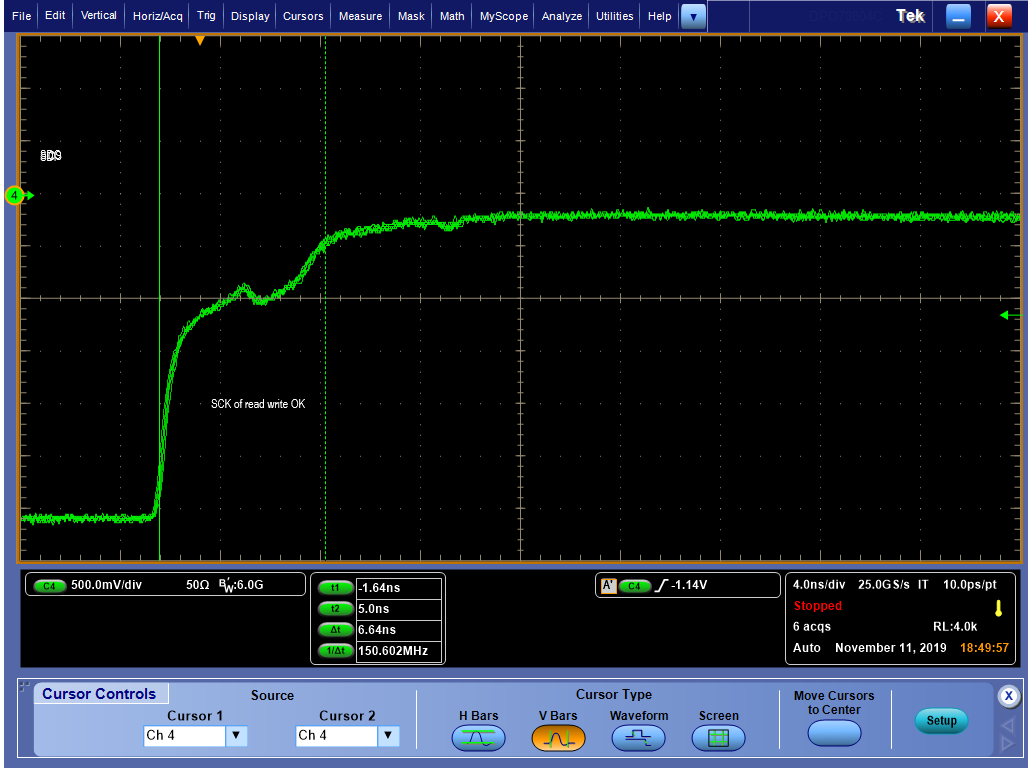

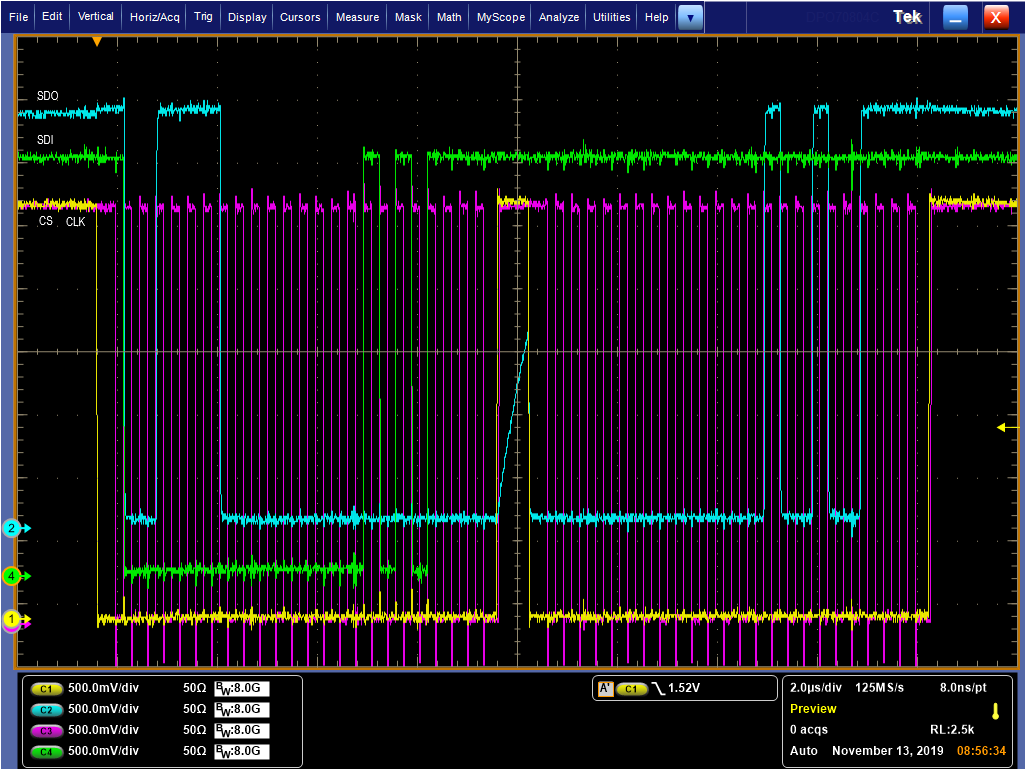

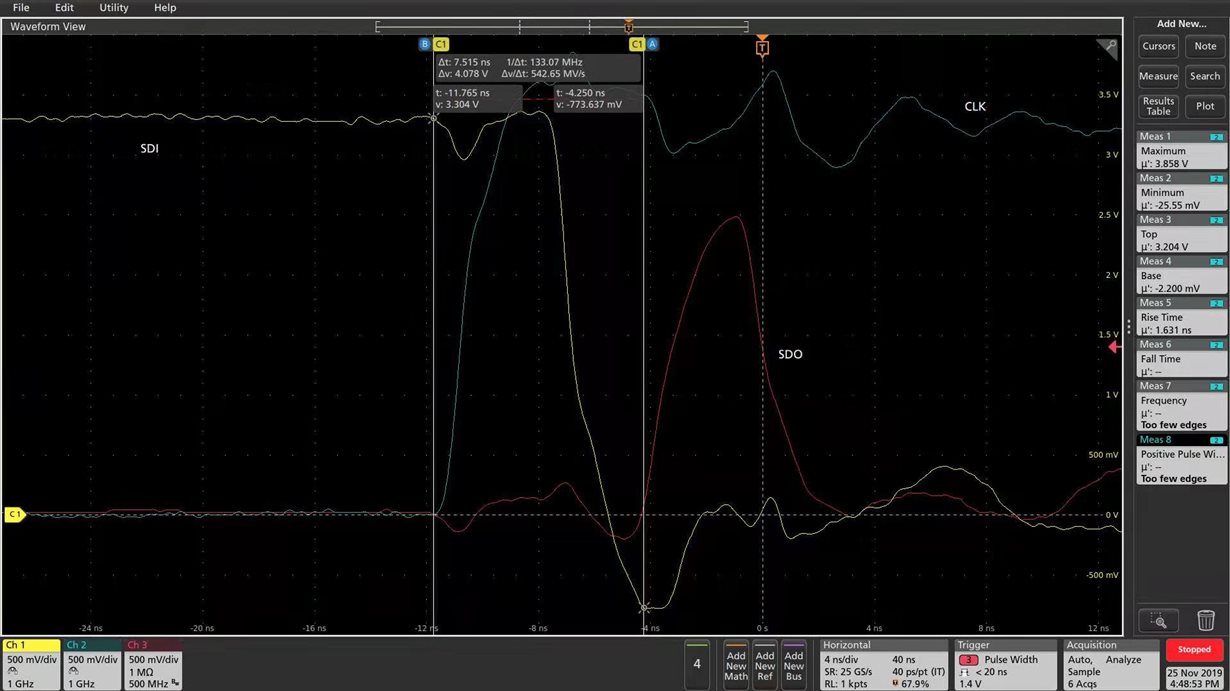

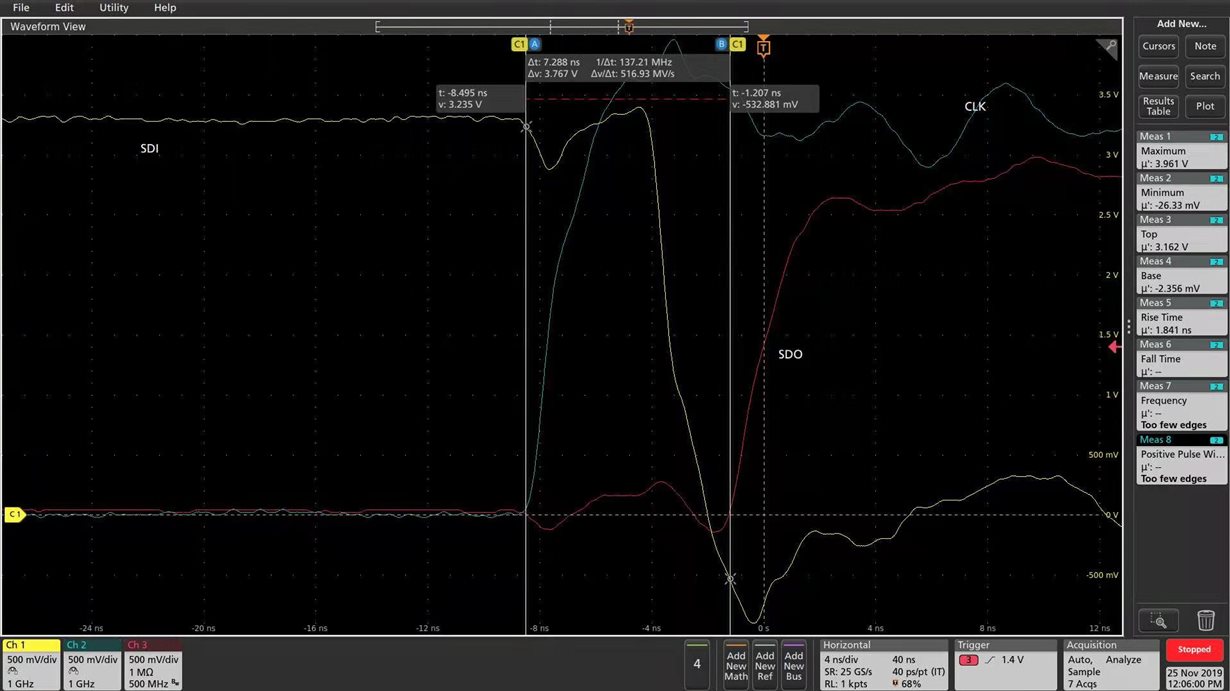

the FPGA SPI code should matter, bu I can't locate it, here is the full waveform of reading reg0:

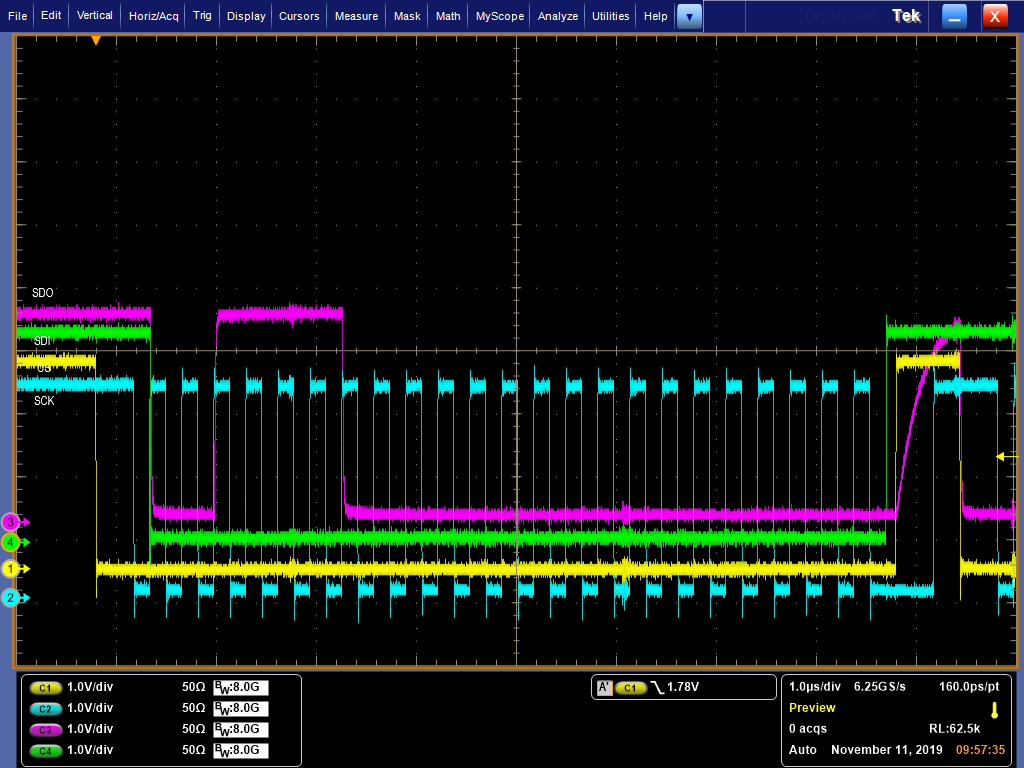

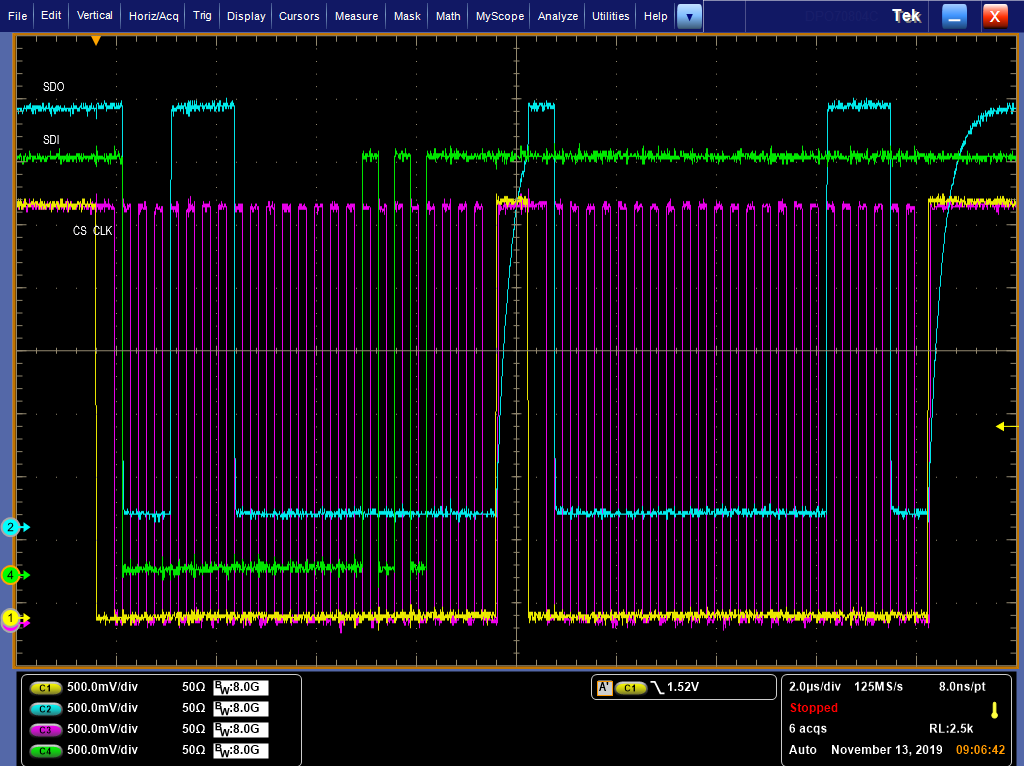

and the zoom in of waveform above: