Other Parts Discussed in Thread: REF3430, OPA320

Hello, we interfaced the ADS8332 with an LPC1857 (NXP) using the SSP0.

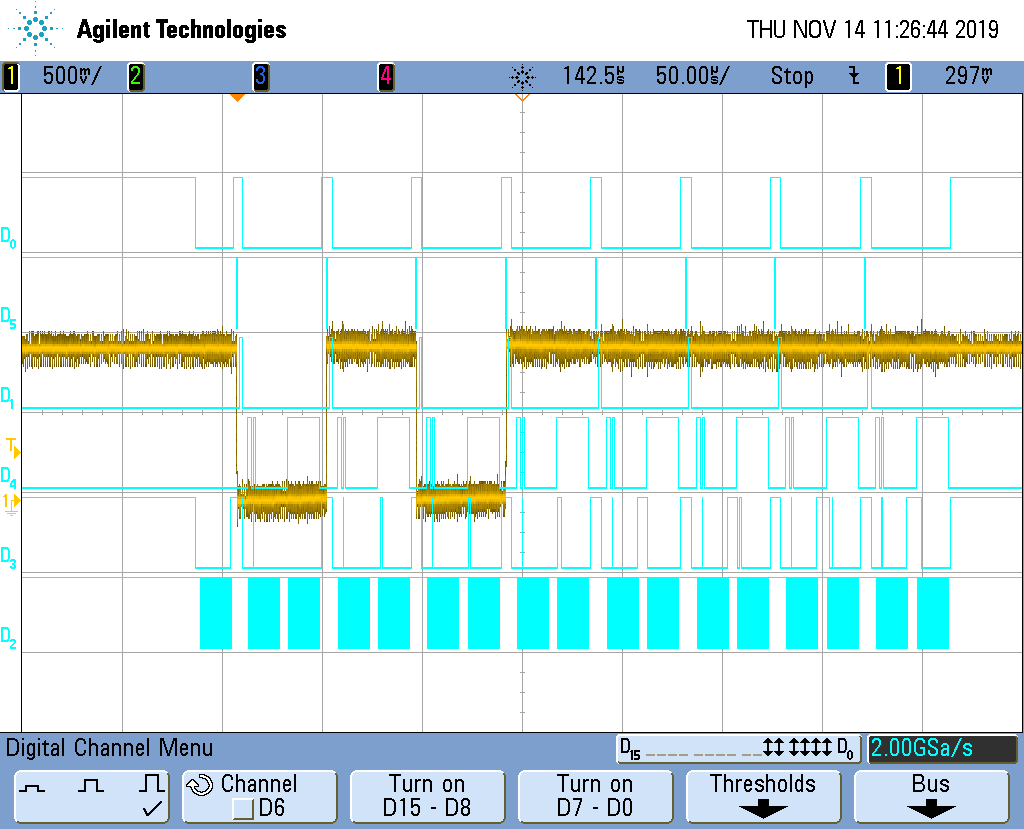

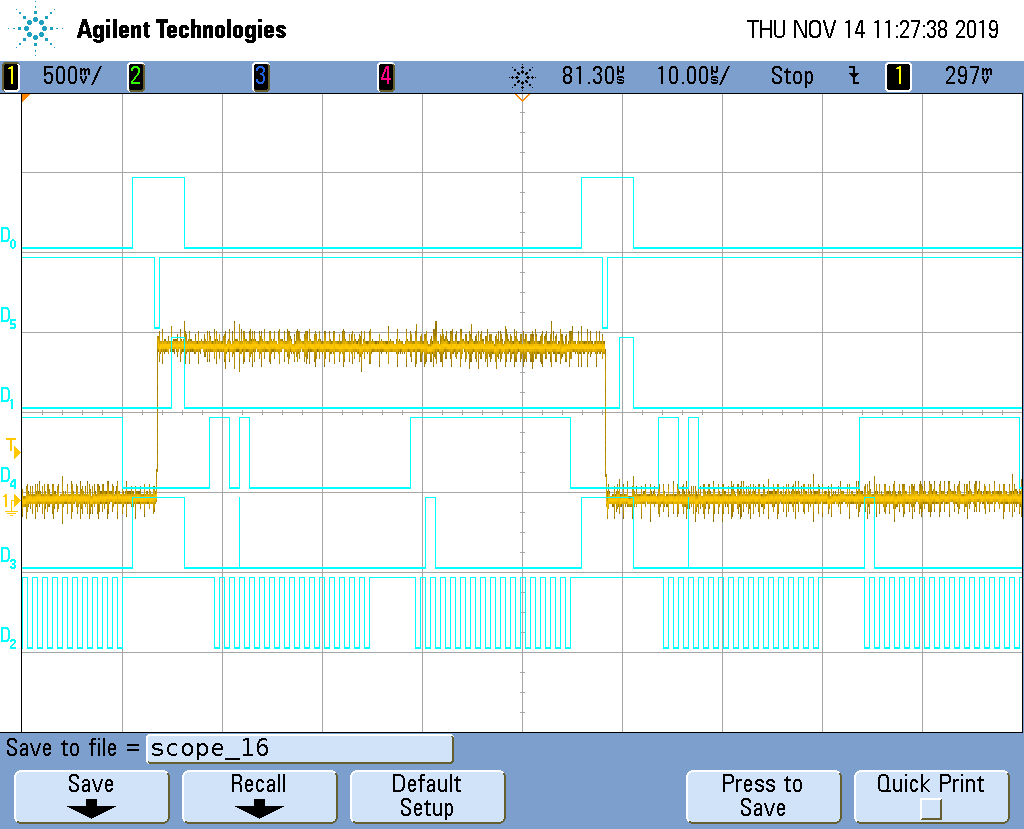

We can read/write the CFG register. The last attempt was made with the CFG written at 0x0F37.

We use the manual trigger (signal CONVST, transition HIGH-LOW-HIGH, width 1us). We respect the timing between EOC and CS.

We use the tag mode and we can read the value of tag (0 to 7) in the sequence of data read by SPI.

But the converted value is always 0.

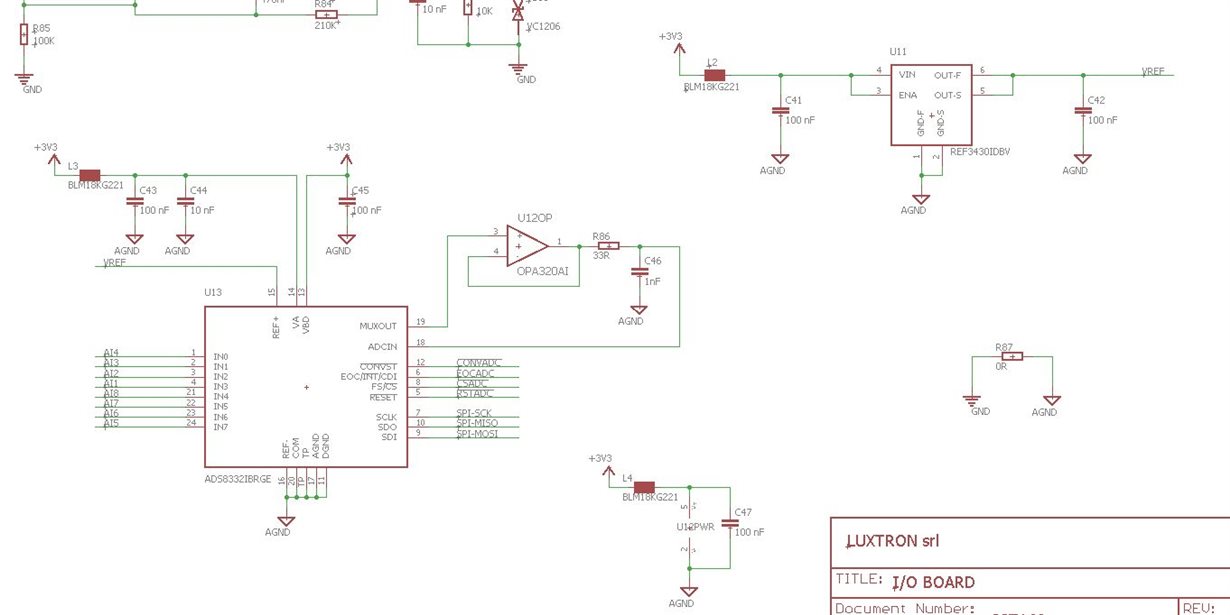

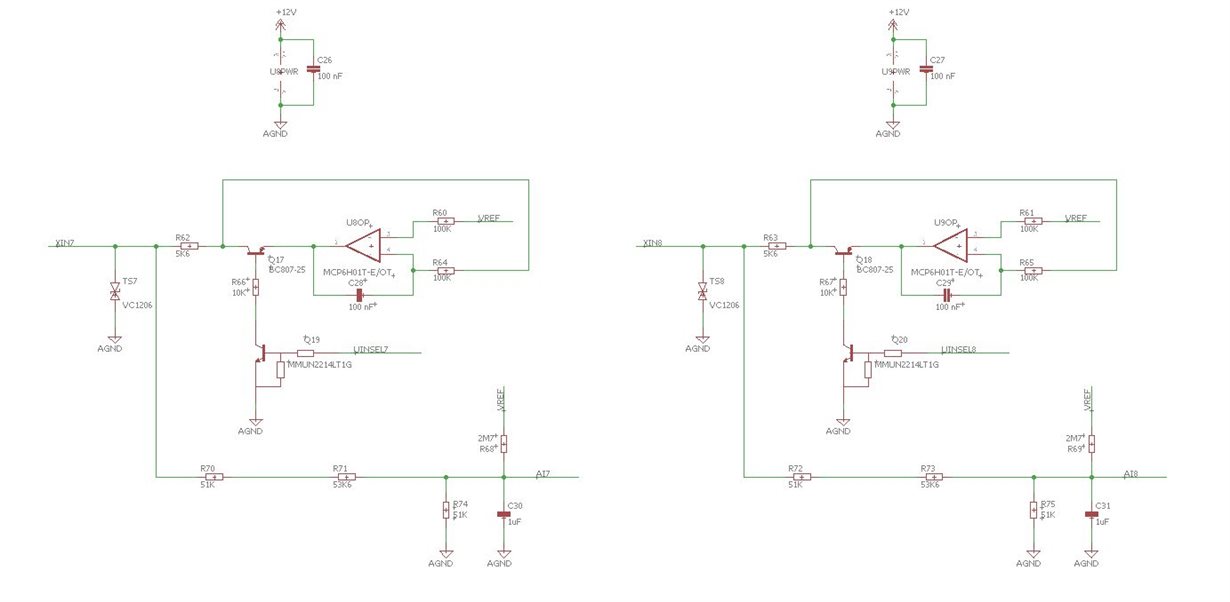

Below I insert the ADS8332 input and connection scheme.

What could be the reason why we read all the channels at 0?

Thank you very much in advance for your help.

Andrea