Other Parts Discussed in Thread: ADC32RF44, , LMX2582, ADC32RF45

Hi,

We currently have ADC32RF44EVM attached to a KCU105 and have downloaded the KCU105 + ADC32RF44 Design Firmware from the TI website.

We have the ADC32RFXX EVM GUI configured with the following settings in the Quick Setup Tab:

- Nyquist Zone = 2nd Nyquist

- Clock Source to ADC = LMX2582 to ADC

- Internal Clk Freq = 2457.6 Msps

- ADC32RF45 Mode = Bypass

- Resolution = 14 bit

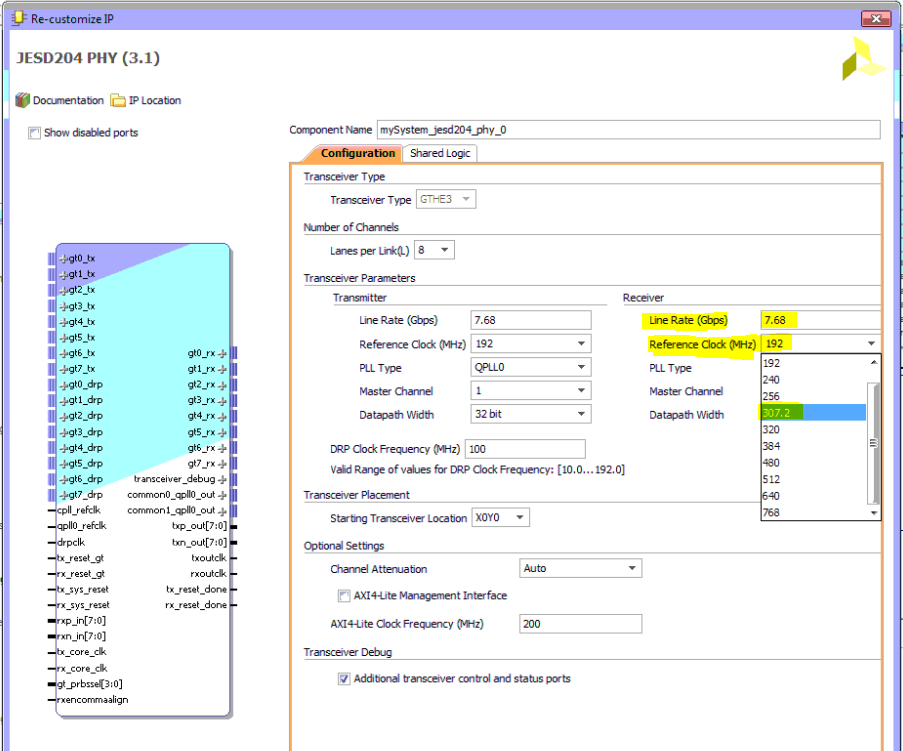

There are no external clock being provided into the ADC32RF44EVM. When you look at the clock output for CLKout 0 it equates to 307.2 MHz. When we open up the KCU105 firmware, the JESD204 PHY Reference Clock is expecting a 192 MHz input. When everything is hooked up and we review the KCU105 LEDs on the Vivado ILA everything appears to be fine. Can someone explain why the KCU105 is syncing and receiving data when the clock it's expecting is not what it is getting. I've also changed the configuration of the GUI to use an Internal Clk Freq of 1536 and generated a 192 MHz clock output on CLKout 0 but that results in the KCU105 no longer syncing to the ADC.

Thanks!

DT