Hi TI Team:

The customer has some problems when using ads5560, please help

Application scenario:

1. Differential input V + - v-input range [- 1.78-1.78];

2. Currently, the maximum input core signal frequency is 1MHz

3. External input single end 16mhz CLK, output use parallel CMOS,data acquisition adopts ADC CLK out

4. use internal reference 1.5V

5. Register configuration is as follows:

Output interface(Rigister6C D4-D3): 00 set cmos interface

Gain:(Rigister68 D3-D0):1000 set gain 0dB

LF.NOISE.SUPPRESSION:(Rigister5D D0):1 set Enable low-frequency noise suppression

Data format:(Register 63 D3):0 Set 2s-complement

REF:(Register 6D D4):0 Set internal refrence

LOW SPEED:(Register 63 D4):1 LOW SPEED mode eabled

STBY:(Register 63 D4):0 Normal operation

Current problems:

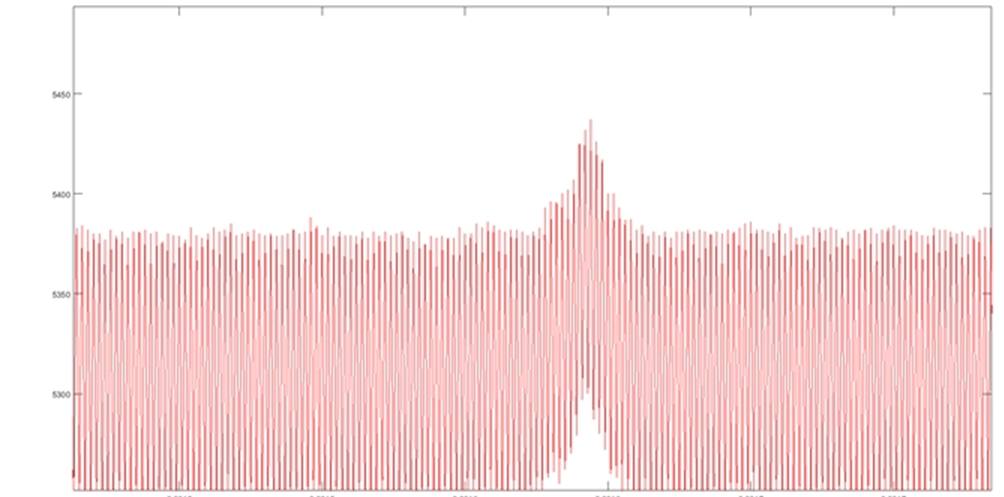

(1) Insufficient dynamic range

Root cause: fixed baseline, size 5400 AD

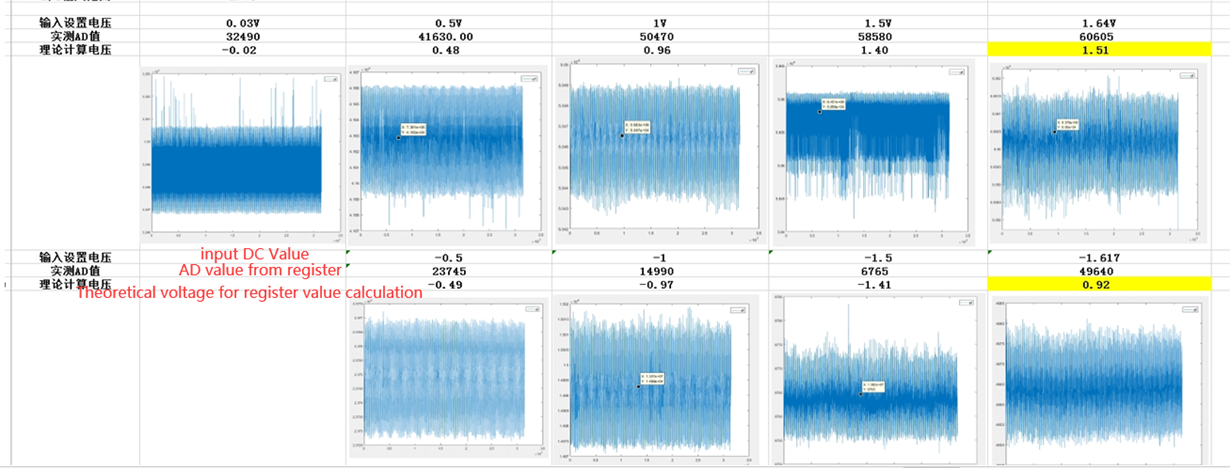

The analog input DC voltage is as follows, and the corresponding measured ad value is as follows

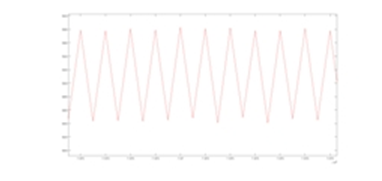

(2) The digital output signal has a fixed frequency of 8MHz noise (shown above after filtering)

after deployment, 8MHz frequency

(3) Question 3: ADC has low noise mode. What is the difference between on and off mode.

Thanks

CQ.LV