Hi, I am using DAC5672 part in my custom board, providing the digital data input to the DAC from the Xilinx Artix-7 FPGA.

- 14-bit Sine Wave digital data is fed to the DAC from FPGA.

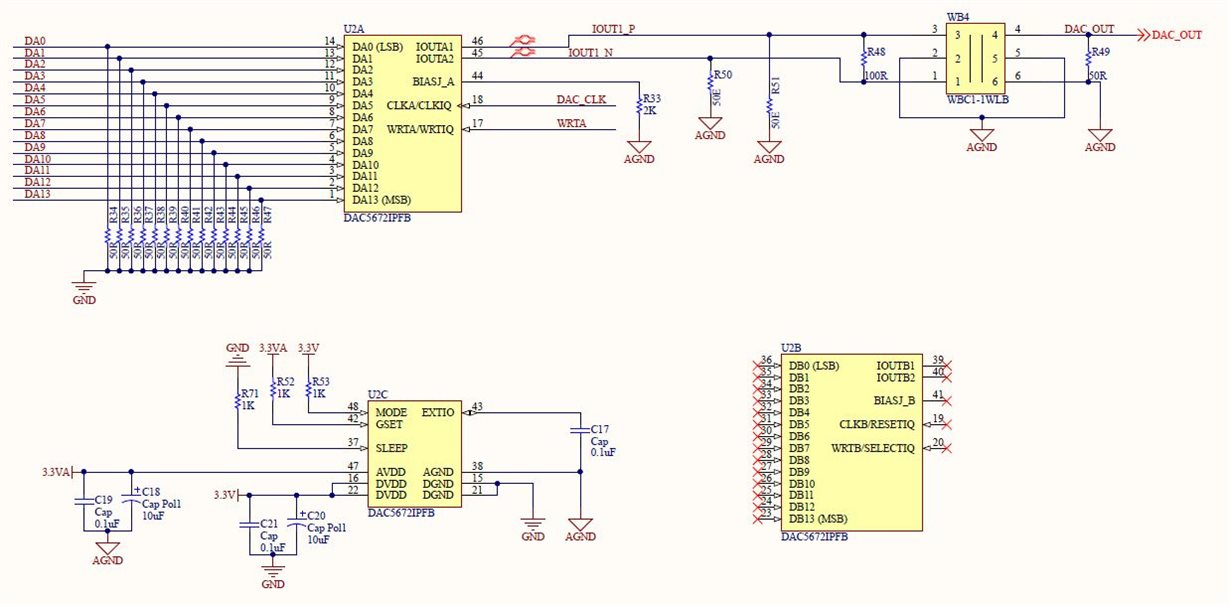

- The DAC is used in Dual Bus mode, only Channel A is being used.

- The input data rate to DAC is 40MSPS; 16 points per sine wave; analog frequency of sine wave is 2.5MHz.

- The DAC Sampling Clock Frequency is 80MHz, which is fed from the FPGA only.

- The "CLOCK" as well as "WRITE_ENABLE" signal are same, continuous free running clocks.

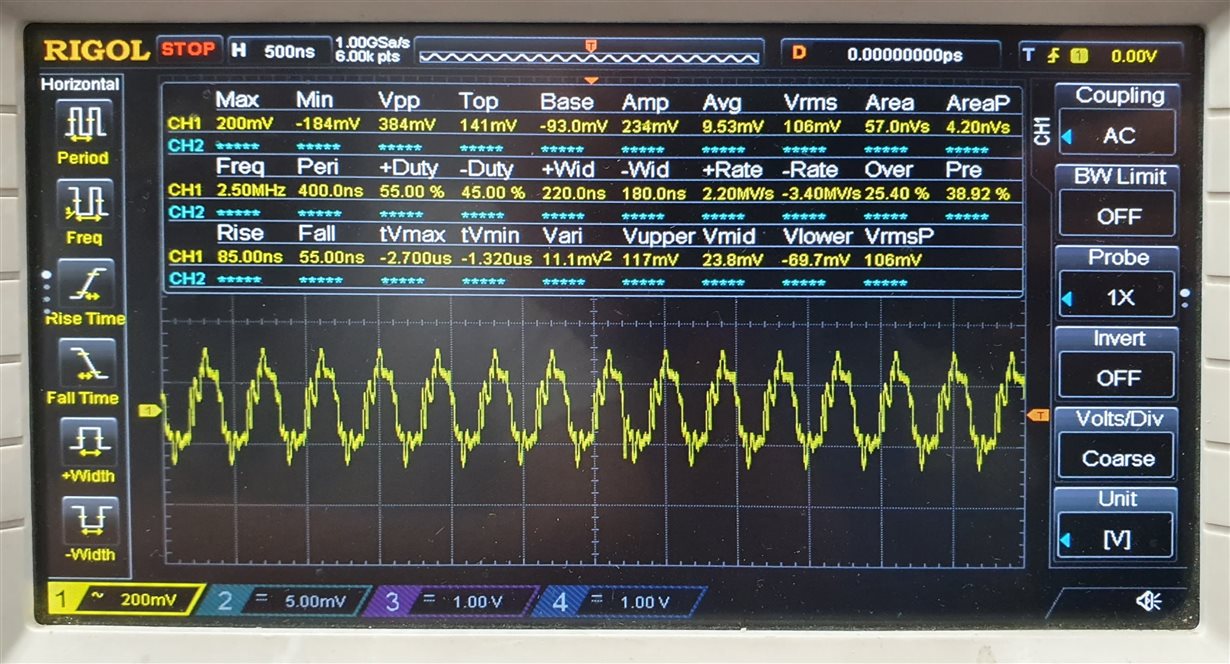

The analog output of the DAC is noisy, having glitches. The oscilloscope snapshot of the same is attached for the reference.

Also, the schematic of the DAC is attached for the reference.

Referring to the below schematic, the input bits DA0......DA13, WRTA, DAC_CLK in the schematic are directly routed from the FPGA. The 100ohm "R48" resistor at the input of the transformer is omitted. The output of the DAC is probed at "DAC_OUT" net, the output of the 1:1 transformer.

Need help in debugging and resolving the issue.

Thanks.