Part Number: ADS8698

Dears,

The MCU is: STM32F103, ADC: ADS8698.

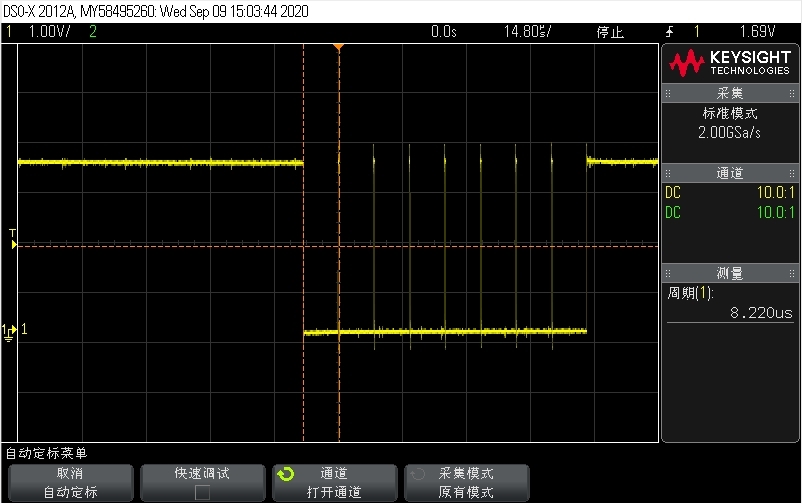

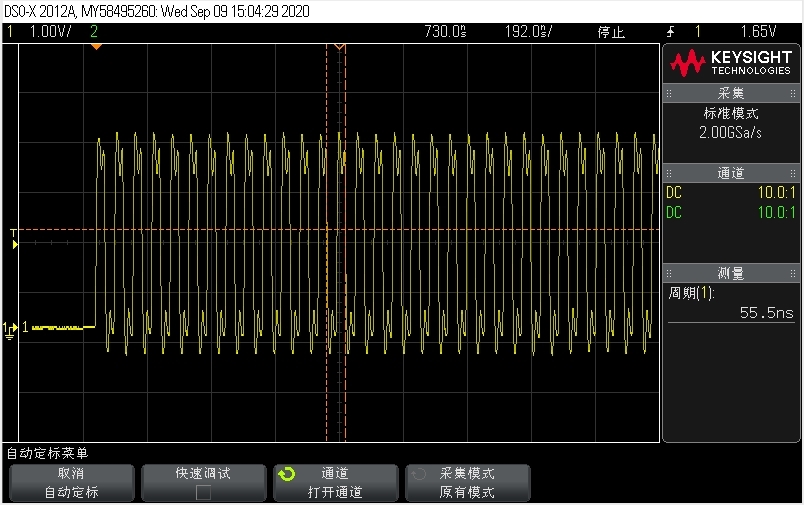

According to the datasheet the maximum throughput is 500Ksps, they are using hardware SPI, the SCLK used is 18MHz, The function they encapsulated is 8bit every time it is sent and read, so a total of 16bit is written to the ADC. 24bit is used for reading, and the CS pin is measured by an oscilloscope. The time for completion of CS pulling down and then pulling up is: 8.2us. They use 8 channels here, so the time for one round of use is: 8.2*8= 65.6us, then the overall throughput is: 1000000/65.6=15243, which is equivalent to the overall throughput: 15KSPS, so they don’t know where the time is used?

Best Regards,

Rock Su