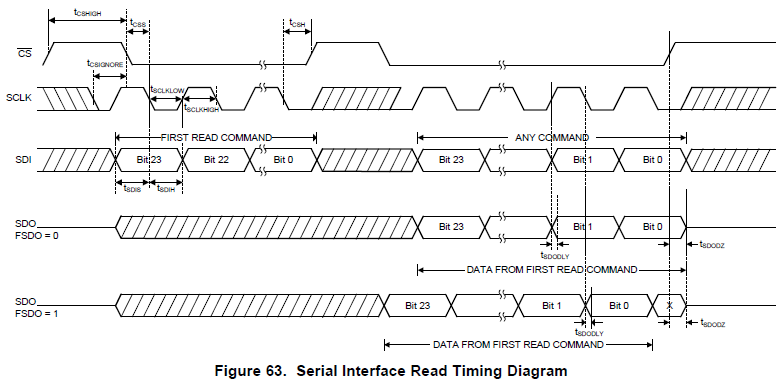

The SBAS871C (August 2017) data sheet illustrates the read timing in Figure 63 but fails to illustrate the start of the read data transaction properly with coordination of CS, SCLK, and read Bit 23.. SCLK is not illustrated properly between the command/data transaction pair; I'm assuming SCLK should be high when CS goes low for both command and data transactions but it's unclear. There is no SDO tristate illustrated between the command and data. Will SDO remain driven during CS high? If FDSO=1, does read bit 23 show up (or remain?) when CS goes low and change to bit 22 after the first falling clock that samples command bit 23?

An illustration from a previous forum question DAC80504: Problems interfacing with DAC80504 shows a more complete timing diagram but with parameters that are not part of the DAC80504 register map.

Does one of the two figures above correspond to the operation of the DAC80504? Are CPOL or CPHA available on the DAC80504?

Many thanks for any insights.

JH