Hello team,

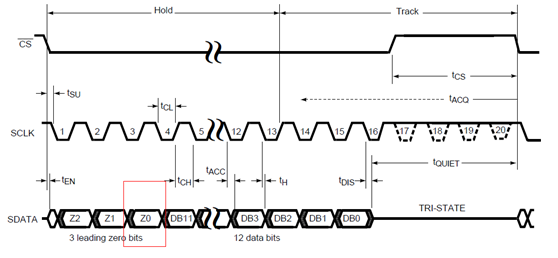

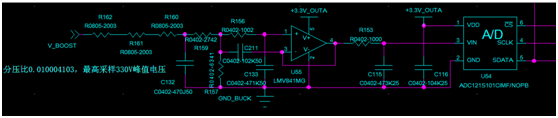

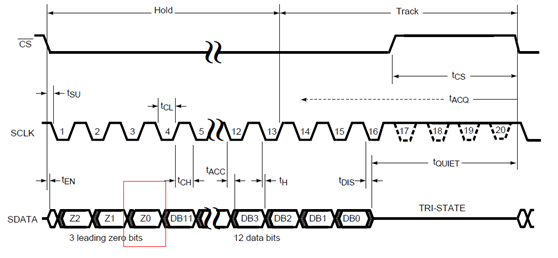

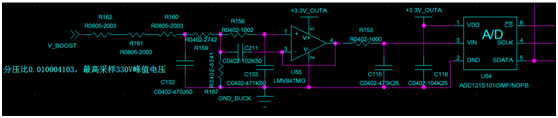

We use the ADC121S101CIMF/NOPB,In the case of normal power supply at room temperature,the ADC sampling output signal seriously deviates from the sampling analog value of the input port,that is a conversion error.We want know why is the anti-interference ability not good? Why will there be a conversion error?

I'm looking forward for your reply,thanks!