Hi,

I have a problem with ADS124S06.

Device is configured as below in sigle shot mode.

static uint8_t m_tx_buf_CONF_1[] = {0x42, 0x00, 0x01, 0x43, 0x00, 0x0F, 0x44, 0x00, 0x39, 0x45, 0x00, 0x02};

// Conf_1: MUXP = AIN0 | MUXN = AIN1 | PGA_EN = 128 |

// Global Chop disable |LL Filter | 100SPS |

// REFP0,REFN0 | Internal reference on

static uint8_t m_tx_buf_CONF_2[] = {0x42, 0x00, 0x23, 0x43, 0x00, 0x0F, 0x44, 0x00, 0x39, 0x45, 0x00, 0x06};

// Conf_2: MUXP = AIN2 | MUXN = AIN3 | PGA_EN = 128 |

// Global Chop disable |LL Filter | 100SPS |

// REFP1,REFN1 | Internal reference on

I read alternately both diferential inputs.

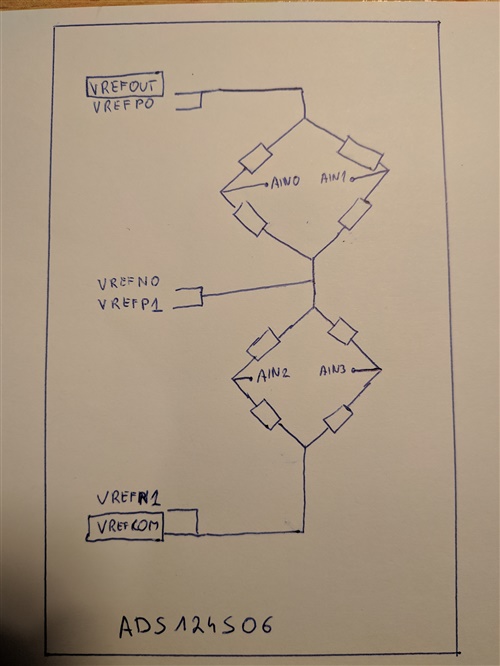

Here is my connection shemat:

And here is output:

Which could be the cause of such spikes ?

Marcin