Other Parts Discussed in Thread: ADS122U04

Folks,

We have implemented the ADS122C04. Power to both AVDD and DVDD are stable for minutes. We pulse the reset pin and ~4us after the rising edge we start writing to the I2C bus.

Per the datasheet this should work:

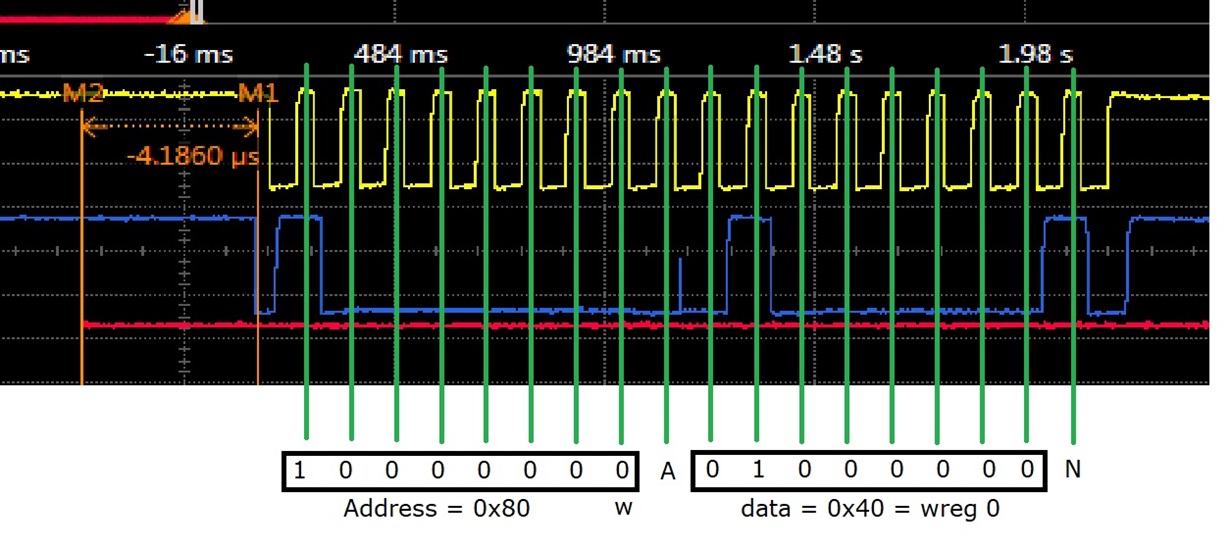

But we're getting NACK's when writing to the register pointer. For example, here is an example scope shot writing to device address 0x40h (7-bit addressing) and register 0x40h (WREG).

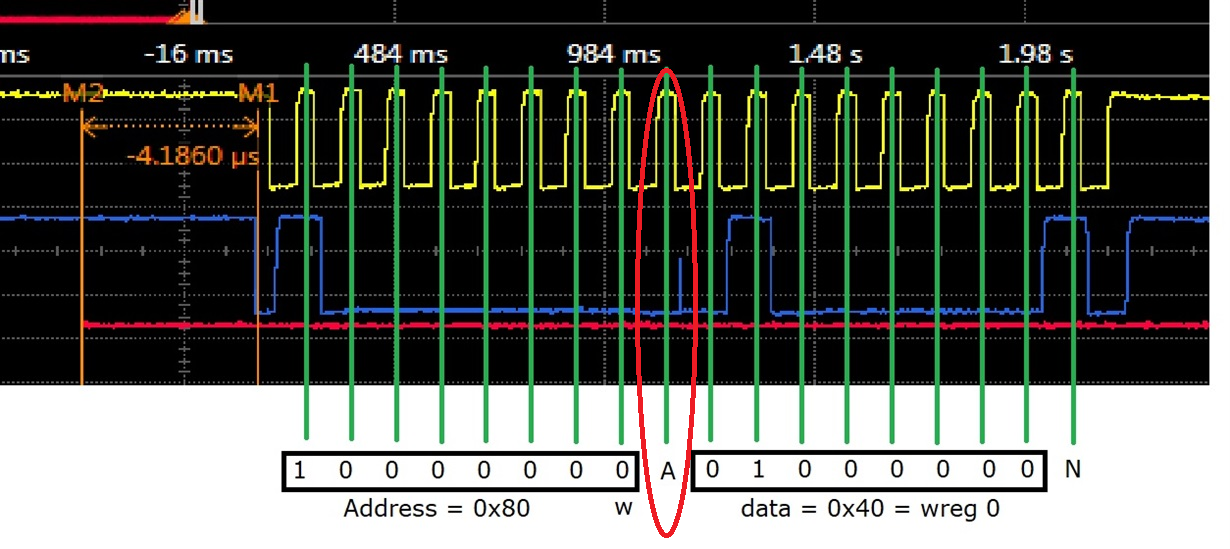

Zooming in a little we see the following:

This matches section 8.5.3.7 of the datasheet:

Increasing the time wait time to >25us, seems to solve this problem.

We suspect that the required delay is closer to the TIMEOUT period as specified in the datasheet. In the case of normal clock mode (256kHz), this would be 14000 x (1/256kHz) ~= 54.7us. We also suspect that the datasheet may have a typo; spec'ing td(RSSTA) in ns as opposed to the correct us.

Looking forward to a little clarification on this subject.

Don