HI,

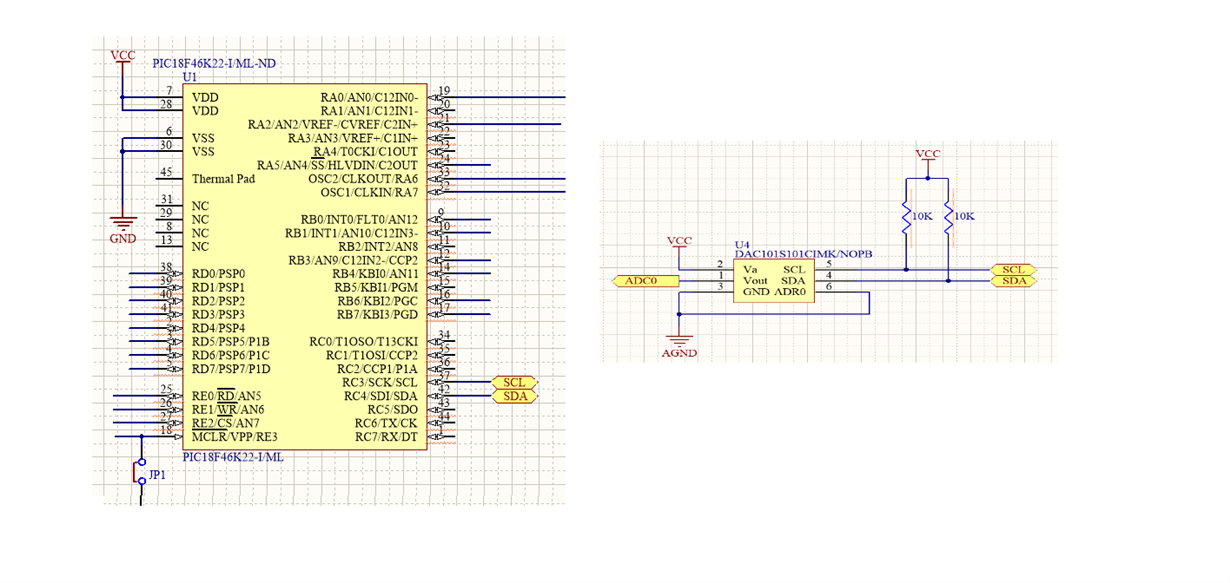

I have problem communicating with the DAC. ADR0 is connected to ground and im using chip address 0001101.

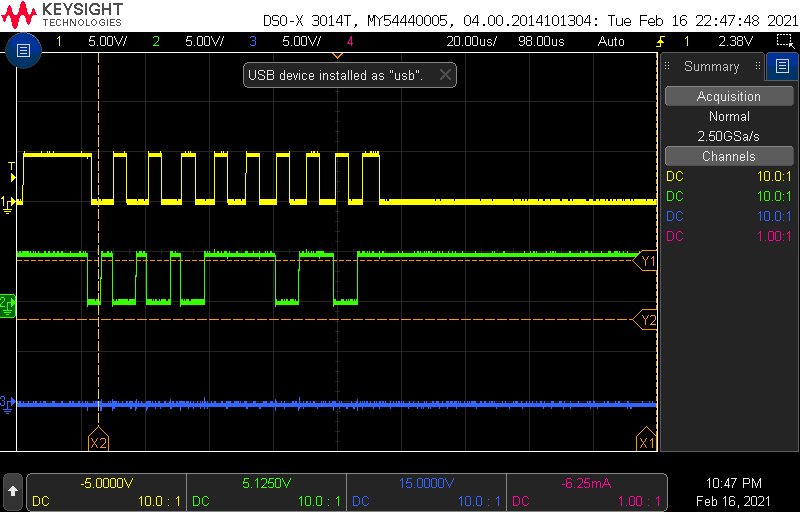

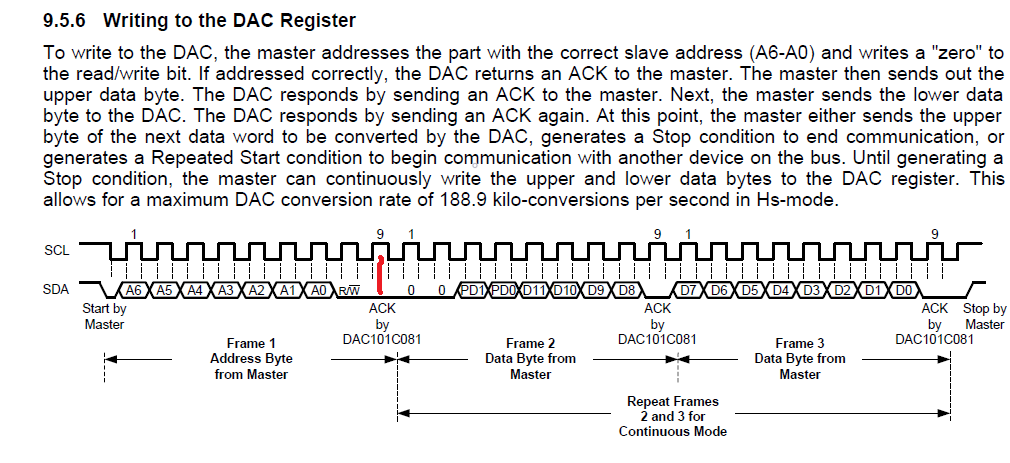

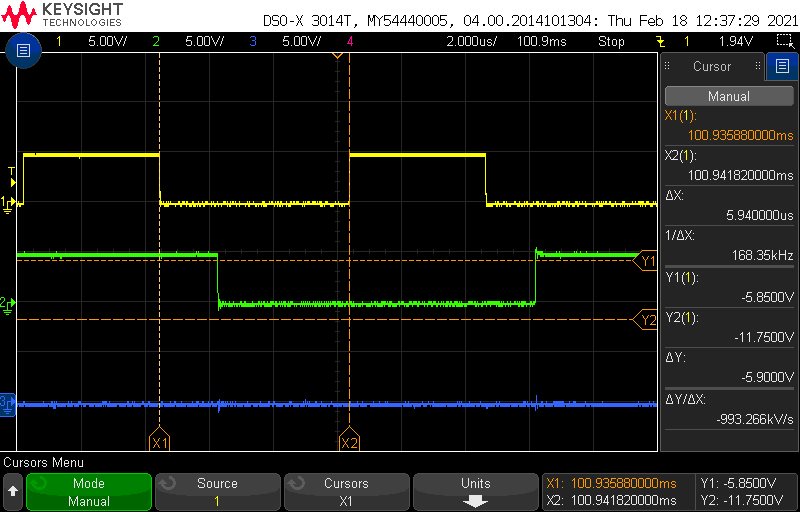

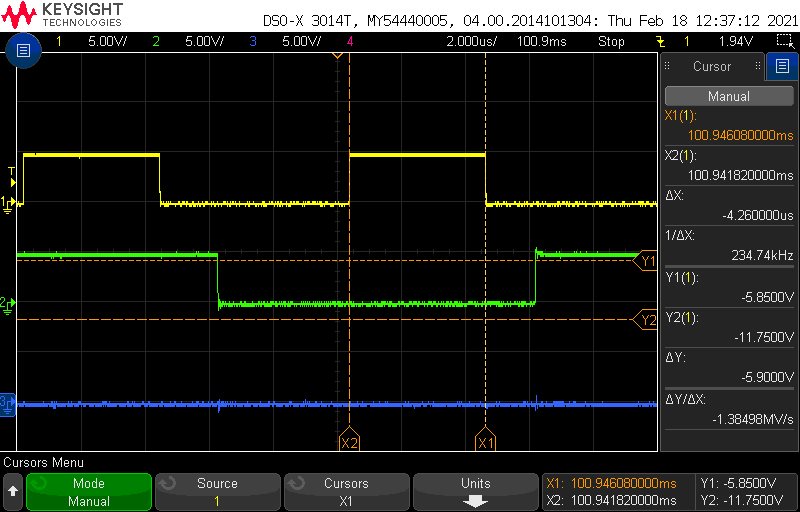

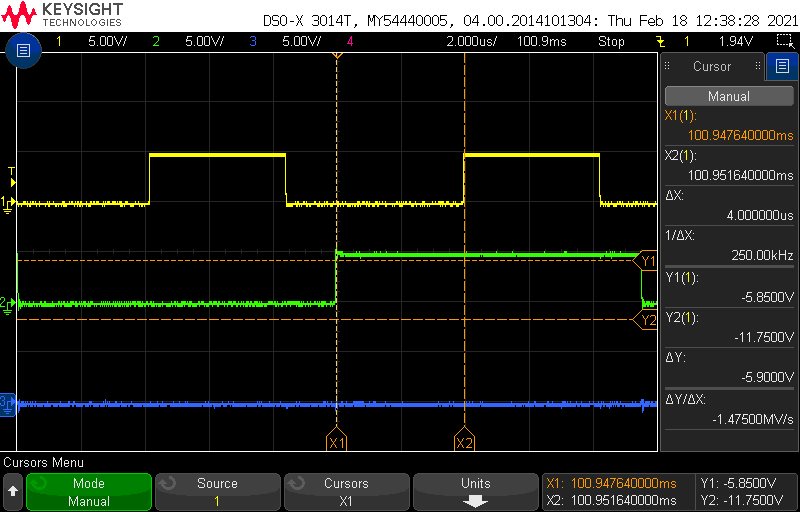

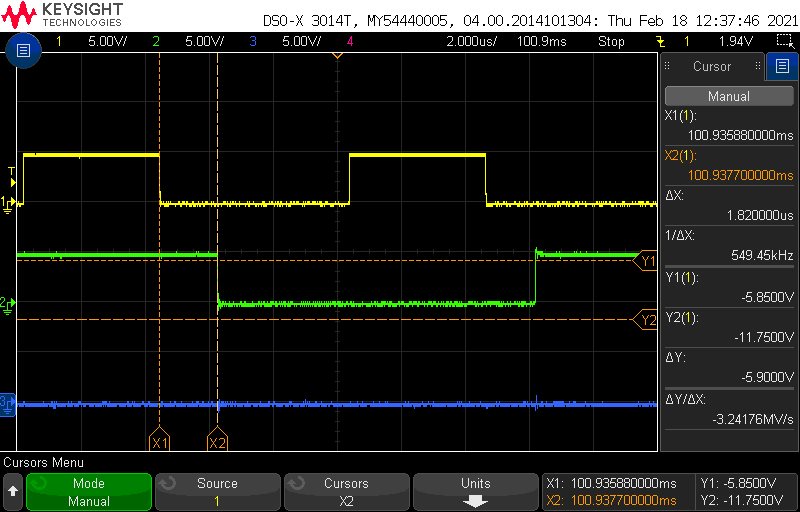

the communication is speeding at 100KHz, and signals / timing seems to be matching as per spec, but the DAC output stays to 0...

Question, should the DAC be sending a NAK SDA to 1 if the chip address is not the good one? because whatever the address im sending to it at the moment, the DAC returns ACK, SDA to 0. I did swap the part in case... same issue.

Thanks for your support!