Other Parts Discussed in Thread: ADS131A04, ADS1018

All:

I am not able to receive an ACK on UNLOCK.

I was able to trace the TIVA interaction with the ADS131a04, and it showed the proper responses to commands.

When I connect an external microprocessor and try to drive the SPI lines, I receive READY, but I do not receive a 0x655 from UNLOCK.

I have 6-inch lines between my board and the EVM: Ground, MOSI, MISO, CS, SCLK.

I have set MO,M1,M2 for 32-bit words, and switched S4 to manual.

I have put a jumper on JP1 to disable processor.

I send "00000000" and see READY.

I send "06550000" and do not see anything other than READY.

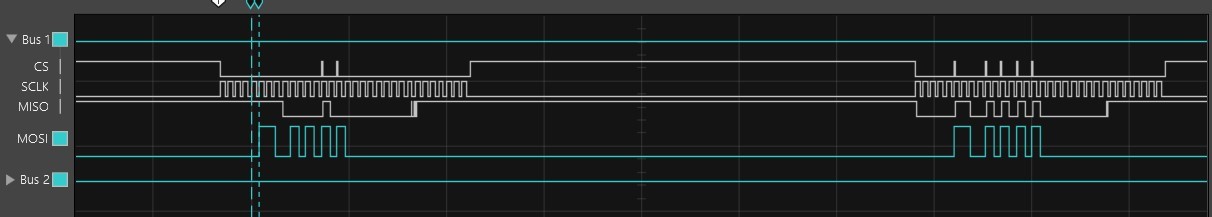

I am using 12.5 MHz SCLK, and the waveform looks correct, except for some "glitches" (However, I was able to connect to ADS1018 with same setup and I was able to receive data.)

Not sure what else to say - I know that the SCLK waveform is not 50% duty cycle (more like 30%) - if I am able to get to 50% would that help?

Also, I am thinking of using twisted-pair for each of the 4 connections. I did twist GND with SCLK and that appeared to clean up noise on that line.

Given that the input clock to the device is 16.384 MHz, is 12.5 MHz too fast?

Regards,

Todd Anderson