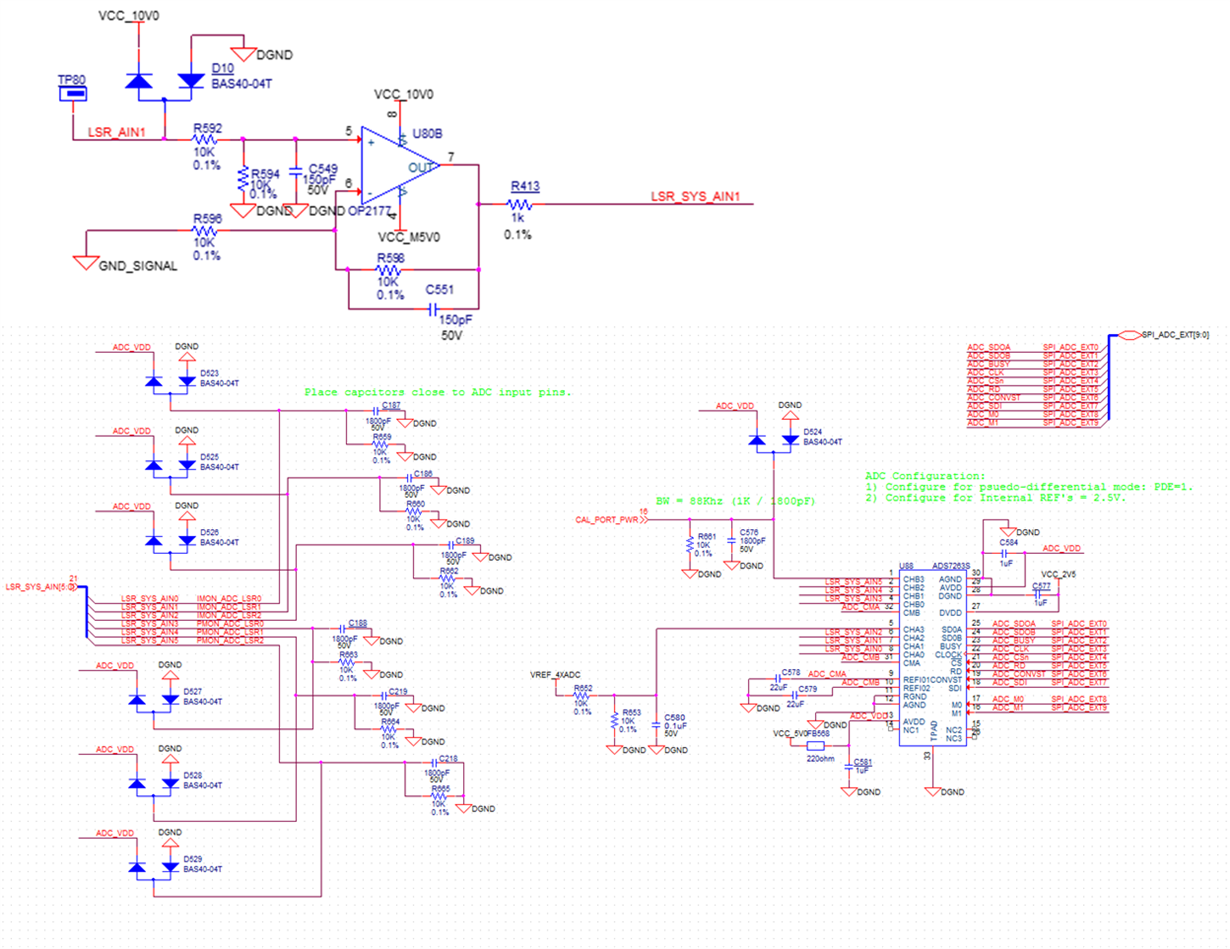

For my application, I have an ADS7263 configured for 8 single ended 0-5V input channels. To use the ADC in single ended mode, the REF outputs (set for 2.5V) are connected to the CMA and CMB inputs. The sample rate is 250K samples per second. The good news is that the basic functionality seems to work as intended. The only issue is that there is a large analog offset of about 0.08 volts on each of the input channels when the actual value is 0 volts. The ADC value for an input of 2.49 volts matches the expected value (half scale) almost perfectly - within 0.1%. I have verified the supply voltages (5.0V for AVDD and 2.5V for DVDD) as well as the value of the references and common mode inputs (very close to 2.4999 volts). While the apparent error / offset for 0 volt input is not huge with respect to full scale (about 1%), I was expecting the error to be much smaller. Please take a look and let me know if you can help me sort out what is causing the large offset voltage.

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.